# GSC3280 用户手册-精简版

2013年6月 版本号: 3.0

北京神州龙芯集成电路设计有限公司 BLX IC Design Co., Ltd

# 目录

| Ħ | 求   |                      |       |

|---|-----|----------------------|-------|

| 冬 | 目录  |                      | XIV   |

| 表 | 目录  |                      | XVIII |

| 1 | 产品村 | 概览                   | 1     |

|   | 1.1 | 产品简介                 | 1     |

|   | 1.2 | . 功能特性               | 2     |

|   | 1.3 | ;结构框图                | 4     |

| 2 | 存储图 | 空间                   | 6     |

|   | 2.1 | 地址映射                 | 6     |

|   | 2.2 | ! 片内存储器              | 8     |

|   | 2.3 | 3 片外存储器              | 8     |

|   |     | 2.3.1 DDR2 存储器       | 8     |

|   |     | 2.3.2 NAND Flash 存储器 | 8     |

|   |     | 2.3.3 NOR Flash 存储器  | 8     |

|   |     | 2.3.4 SPI Flash 存储器  | 9     |

|   |     | 2.3.5 静态存储器          | 9     |

| 3 | 龙芯  | 处理器                  | 10    |

|   | 3.1 | . 概述                 | 10    |

|   | 3.2 | ! 功能特性               | 10    |

|   | 3.3 | 3 结构框图               | 10    |

|   |     | · 流水线                |       |

|   | 3.5 | 5 寄存器                | 11    |

|   | 3.6 | 5 存储管理               | 11    |

|   |     | 3.6.1 工作模式           | 11    |

|   |     | 3.6.1.1 逻辑地址空间       |       |

|   |     | 3.6.1.2 用户模式         |       |

|   |     | 3.6.1.3 监管模式         |       |

|   |     | 3.6.1.4 内核模式         | 15    |

|   |     | 3.6.1.5 调试模式         | 16    |

|   |     | 3.6.2 TLB            |       |

|   |     | 3.6.3 虚实地址转换         |       |

|   | 3.7 | '高速缓存                | 21    |

|   |     | 3.7.1 概述             |       |

|   |     | 3.7.2 组织结构           |       |

|   |     | 3.7.3 替换策略           |       |

|   |     | 3.7.4 cache 操作       |       |

|   | 3.8 | 3 例外处理               |       |

|   |     | 3.8.1 精确例外           |       |

|   |     | 3.8.2 例外优先级          |       |

|   |     | 3.8.3 例外处理入口         | 25    |

| 3.8.4 通用例外处理                    | 26 |

|---------------------------------|----|

| 3.8.5 复位例外处理                    | 27 |

| 3.8.6 调试例外处理                    | 27 |

| 3.9 CPO 协处理器                    | 28 |

| 3.9.1 概述                        | 28 |

| 3.9.2 CPO 寄存器列表                 | 28 |

| 3.9.3 CPO 寄存器描述                 | 29 |

| 3.9.3.1 CPO 寄存器 0: Index        | 29 |

| 3.9.3.2 CPO 寄存器 1: Random       |    |

| 3.9.3.3 CPO 寄存器 2/3: EntryLoO/1 |    |

| 3.9.3.4 CPO 寄存器 4: Context      |    |

| 3.9.3.5 CPO 寄存器 5: PageMask     | 31 |

| 3.9.3.6 CP0 寄存器 6: Wired        |    |

| 3.9.3.7 CP0 寄存器 7: BadVaddr     |    |

| 3.9.3.8 CPO 寄存器 9: Count        | 33 |

| 3.9.3.9 CPO 寄存器 10: EntryHi     |    |

| 3.9.3.10 CP0 寄存器 11: Compare    |    |

| 3.9.3.11 CPO 寄存器 12: Status     |    |

| 3.9.3.12 CP0 寄存器 13: Cause      |    |

| 3.9.3.13 CPO 寄存器 14: EPC        |    |

| 3.9.3.14 CPO 寄存器 15: PRId       |    |

| 3.9.3.15 CPO 寄存器 16: Config     |    |

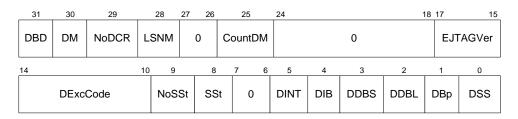

| 3.9.3.16 CPO 寄存器 23: Debug      |    |

| 3.9.3.17 CPO 寄存器 24: DEPC       |    |

| 3.9.3.18 CPO 寄存器 28: TagLo      |    |

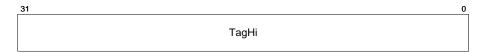

| 3.9.3.19 CPO 寄存器 29: TagHi      |    |

| 3.9.3.20 CPO 寄存器 30: ErrorEPC   |    |

| 3.9.3.21 CPO 寄存器 31: DeSave     |    |

| 3.10 片上调试特性                     |    |

| 3.11 指令集                        |    |

| 3.11.1 指令集概览                    |    |

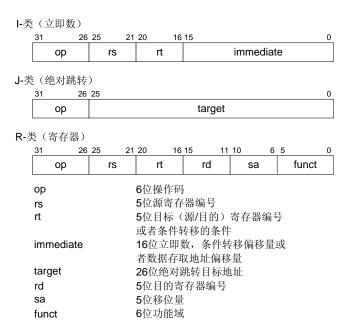

| 3.11.1.1 指令格式                   |    |

| 3.11.1.2 数据存取指令                 |    |

| 3.11.1.3 数据运算指令                 |    |

| 3.11.1.4 转移指令                   |    |

| 3.11.1.5 控制指令                   |    |

| 3.11.1.6 协处理器指令                 |    |

| 3.11.2 指令集汇总                    |    |

| 3.11.3 指令描述                     |    |

| 3.11.3.1 ADD                    |    |

| 3.11.3.2 ADDII                  |    |

| 3.11.3.3 ADDIU                  |    |

| 3.11.3.4 ADDU                   |    |

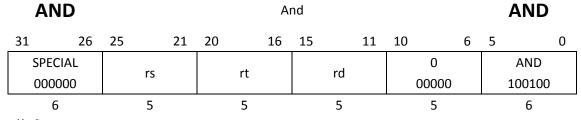

| 3.11.3.5 AND                    | 49 |

| 3.11.3.6 ANDI     | 50 |

|-------------------|----|

| 3.11.3.7 BEQ      | 50 |

| 3.11.3.8 BEQL     | 51 |

| 3.11.3.9 BGEZ     | 51 |

| 3.11.3.10 BGEZAL  | 52 |

| 3.11.3.11 BGEZALL | 52 |

| 3.11.3.12 BGEZL   | 53 |

| 3.11.3.13 BGTZ    |    |

| 3.11.3.14 BGTZL   | 54 |

| 3.11.3.15 BLEZ    | 54 |

| 3.11.3.16 BLEZL   | 55 |

| 3.11.3.17 BLTZ    |    |

| 3.11.3.18 BLTZAL  | 56 |

| 3.11.3.19 BLTZALL | 57 |

| 3.11.3.20 BLTZL   | 57 |

| 3.11.3.21 BNE     | 58 |

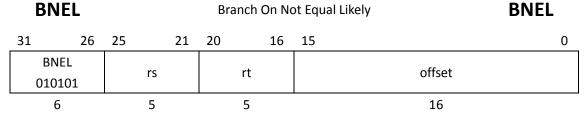

| 3.11.3.22 BNEL    | 58 |

| 3.11.3.23 BREAK   | 59 |

| 3.11.3.24 CACHE   |    |

| 3.11.3.25 DERET   | 61 |

| 3.11.3.26 DIV     | 61 |

| 3.11.3.27 DIVU    | 62 |

| 3.11.3.28 ERET    | 62 |

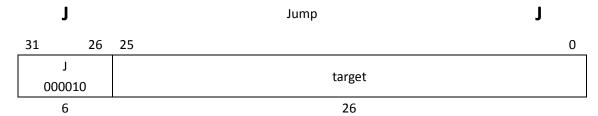

| 3.11.3.29 J       | 63 |

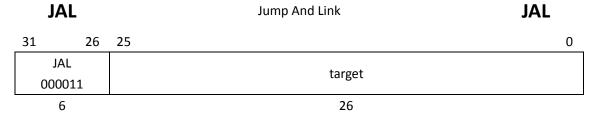

| 3.11.3.30 JAL     | 63 |

| 3.11.3.31 JALR    | 64 |

| 3.11.3.32 JR      | 64 |

| 3.11.3.33 LB      | 65 |

| 3.11.3.34 LBU     | 65 |

| 3.11.3.35 LH      | 66 |

| 3.11.3.36 LHU     | 66 |

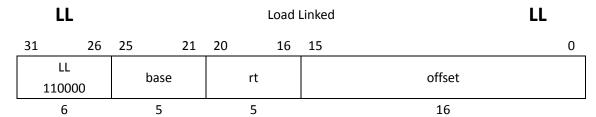

| 3.11.3.37 LL      | 67 |

| 3.11.3.38 LUI     | 68 |

| 3.11.3.39 LW      | 68 |

| 3.11.3.40 LWL     | 69 |

| 3.11.3.41 LWR     | 70 |

| 3.11.3.42 MFC0    | 71 |

| 3.11.3.43 MFHI    | 72 |

| 3.11.3.44 MFLO    | 72 |

| 3.11.3.45 MTC0    | 72 |

| 3.11.3.46 MTHI    | 73 |

| 3.11.3.47 MTLO    | 73 |

| 3.11.3.48 MULT    | 73 |

| 3 11 3 49 MIJITU  | 74 |

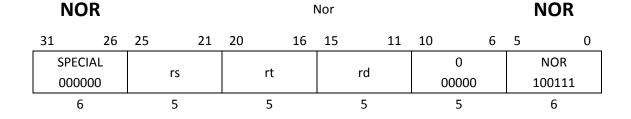

|   | 3.11.3.50 NOR     | 74 |

|---|-------------------|----|

|   | 3.11.3.51 OR      | 75 |

|   | 3.11.3.52 ORI     | 75 |

|   | 3.11.3.53 SB      | 76 |

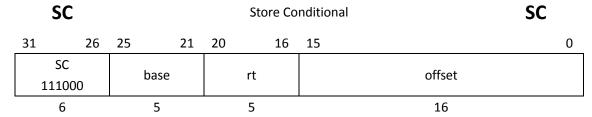

|   | 3.11.3.54 SC      | 76 |

|   | 3.11.3.55 SDBBP   | 77 |

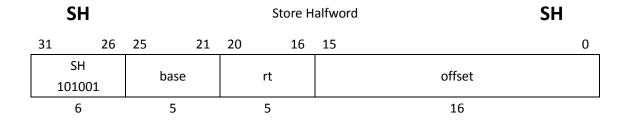

|   | 3.11.3.56 SH      | 77 |

|   | 3.11.3.57 SLL     | 78 |

|   | 3.11.3.58 SLLV    | 78 |

|   | 3.11.3.59 SLT     | 79 |

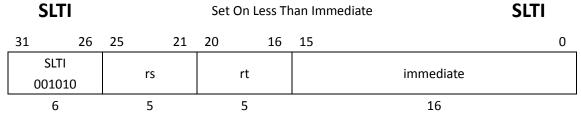

|   | 3.11.3.60 SLTI    | 79 |

|   | 3.11.3.61 SLTIU   | 80 |

|   | 3.11.3.62 SLTU    | 80 |

|   | 3.11.3.63 SRA     | 81 |

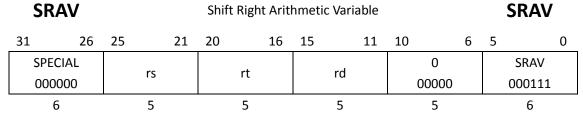

|   | 3.11.3.64 SRAV    | 81 |

|   | 3.11.3.65 SRL     | 82 |

|   | 3.11.3.66 SRLV    | 82 |

|   | 3.11.3.67 SUB     | 83 |

|   | 3.11.3.68 SUBU    | 83 |

|   | 3.11.3.69 SW      | 83 |

|   | 3.11.3.70 SWL     | 84 |

|   | 3.11.3.71 SWR     | 85 |

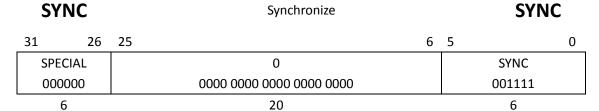

|   | 3.11.3.72 SYNC    | 86 |

|   | 3.11.3.73 SYSCALL | 87 |

|   | 3.11.3.74 TEQ     | 87 |

|   | 3.11.3.75 TEQI    | 87 |

|   | 3.11.3.76 TGE     | 88 |

|   | 3.11.3.77 TGEI    | 88 |

|   | 3.11.3.78 TGEIU   | 89 |

|   | 3.11.3.79 TGEU    | 89 |

|   | 3.11.3.80 TLBP    |    |

|   | 3.11.3.81 TLBR    | 90 |

|   | 3.11.3.82 TLBWI   | 91 |

|   | 3.11.3.83 TLBWR   | 91 |

|   | 3.11.3.84 TLT     | 92 |

|   | 3.11.3.85 TLTI    |    |

|   | 3.11.3.86 TLTIU   | 92 |

|   | 3.11.3.87 TLTU    | 93 |

|   | 3.11.3.88 TNE     |    |

|   | 3.11.3.89 TNEI    |    |

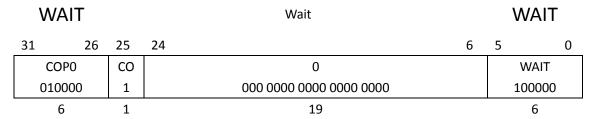

|   | 3.11.3.90 WAIT    |    |

|   | 3.11.3.91 XOR     |    |

|   | 3.11.3.92 XORI    |    |

| 4 | 系统控制              |    |

|   |                   |    |

| 4     | 4.1 概述              | 96  |

|-------|---------------------|-----|

| 4     | 4.2 功能特性            | 96  |

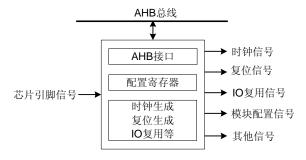

| 4     | 4.3 结构框图            | 96  |

| 4     | 4.4 启动模式            | 96  |

|       | 4.4.1 NAND Flash 启动 | 97  |

|       | 4.4.2 SPI Flash 启动  | 97  |

|       | 4.4.3 NOR Flash 启动  | 97  |

| 4     | 4.5 时钟管理            | 98  |

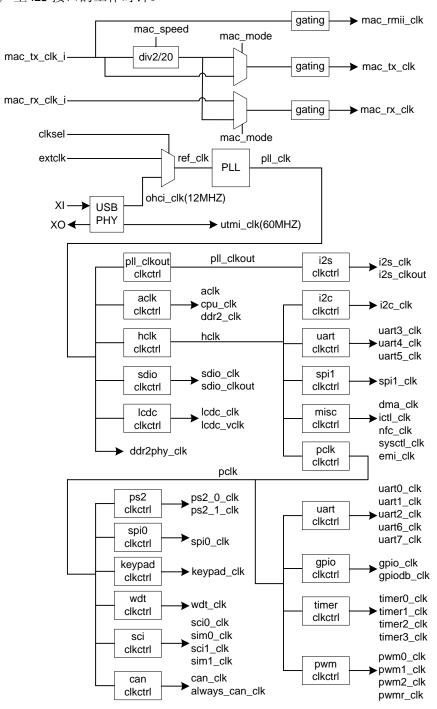

|       | 4.5.1 时钟结构          | 98  |

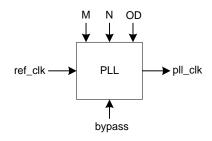

|       | 4.5.2 PLL 配置        | 101 |

|       | 4.5.3 时钟分频          | 102 |

| 4     | 4.6 复位管理            | 103 |

|       | 4.6.1 复位来源          | 103 |

|       | 4.6.2 软件复位          | 103 |

| 4     | 4.7 功耗管理            | 104 |

|       | 4.7.1 模块关闭          | 104 |

|       | 4.7.2 低频运行          | 104 |

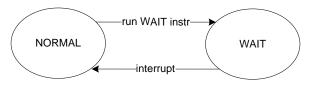

|       | 4.7.3 休眠模式          | 104 |

| 4     | 4.8 IO 复用           | 105 |

| 4     | 4.9 总线错误            | 106 |

| 4     | 4.10 模块配置           | 106 |

| 4     | 4.11 寄存器描述          | 106 |

| 4     | 4.12 编程指导           | 106 |

| 5 DDF | PR2 控制器             | 107 |

| į     | 5.1 概述              | 107 |

| į     | 5.2 引脚描述            | 107 |

| į     | 5.3 功能说明            | 108 |

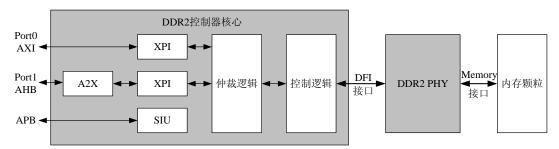

|       | 5.3.1 DDR2 控制器核心    | 109 |

|       | 5.3.1.1 时钟描述        | 109 |

|       | 5.3.1.2 XPI         | 109 |

|       | 5.3.1.3 AHB 接口的数据预取 | 110 |

|       | 5.3.1.4 仲裁逻辑        | 110 |

|       | 5.3.1.5 反压机制        | 111 |

|       | 5.3.1.6 地址映射        | 111 |

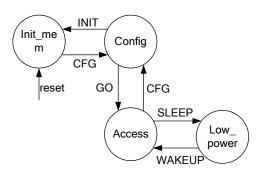

|       | 5.3.1.7 操作状态机       | 112 |

|       | 5.3.1.8 初始化流程       | 113 |

|       | 5.3.2 DDR2 PHY      | 113 |

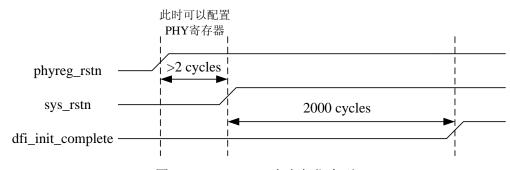

|       | 5.3.2.1 上电复位顺序      | 113 |

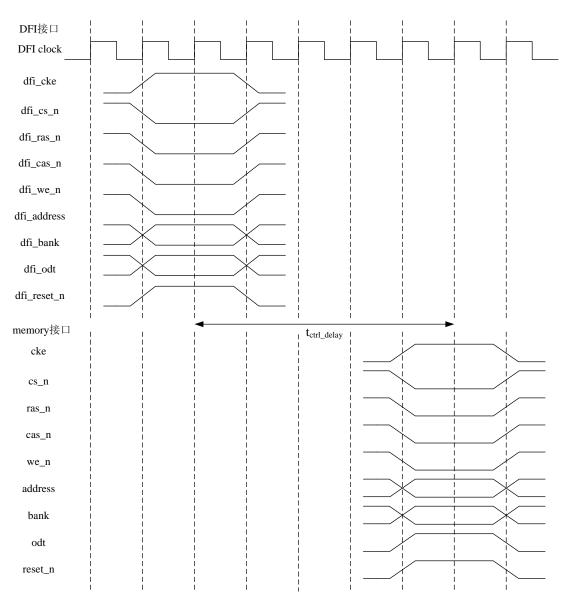

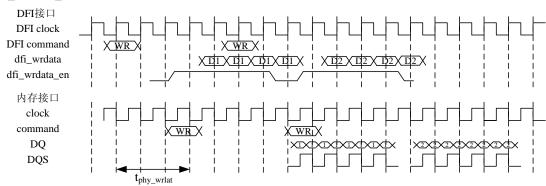

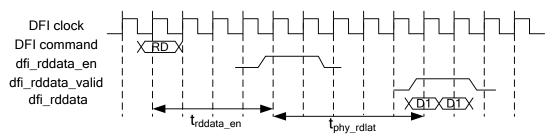

|       | 5.3.2.2 时间参数        |     |

| į     | 5.4 寄存器描述           |     |

| į     | 5.5 编程指导            | 116 |

|       | ND Flash 控制器        |     |

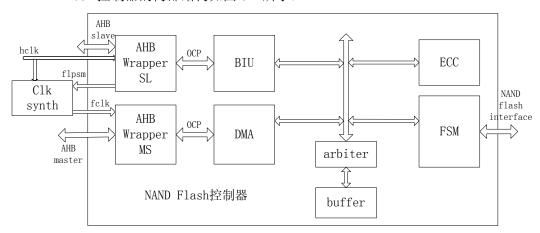

| (     | 6.1 概述              | 117 |

| (     | 6.2 引脚描述            | 117 |

| 6.3      | 功能说明                          | 118 |

|----------|-------------------------------|-----|

|          | 6.3.1 支持协议                    | 118 |

|          | 6.3.2 功能特点                    | 118 |

|          | 6.3.3 功能描述                    | 118 |

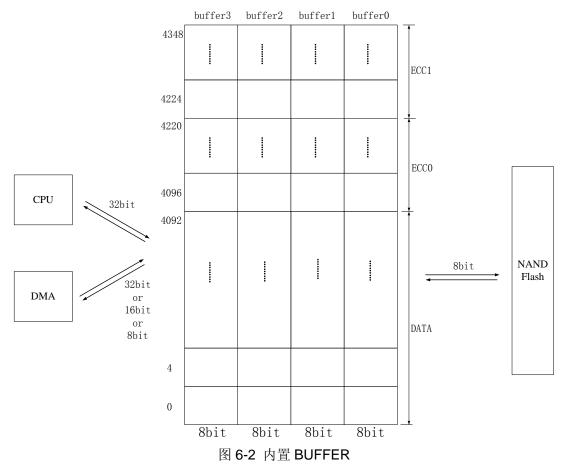

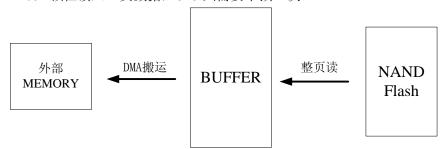

|          | 6.3.4 内部 BUFFER               | 119 |

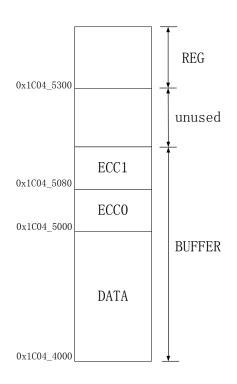

|          | 6.3.5 BUFFER 与寄存器的地址映射关系      | 120 |

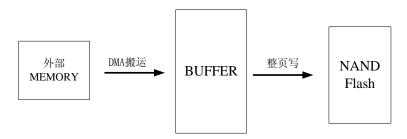

|          | 6.3.6 DMA 操作                  | 121 |

|          | 6.3.7 基本读写操作                  | 122 |

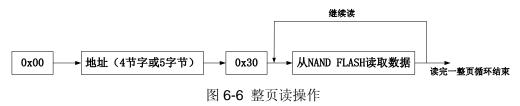

|          | 6.3.7.1 整页读操作(Page Read)      | 125 |

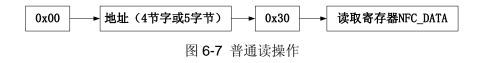

|          | 6.3.7.2 普通读操作(Page Read 1)    | 125 |

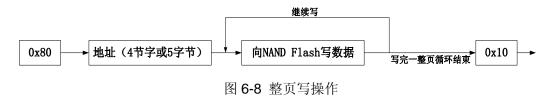

|          | 6.3.7.3 整页写操作(Program Page)   | 125 |

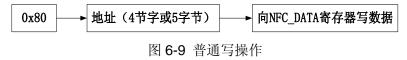

|          | 6.3.7.4 普通写操作(Program Page 1) | 126 |

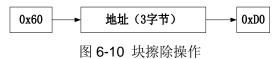

|          | 6.3.7.5 块擦除操作(Block Erase)    | 126 |

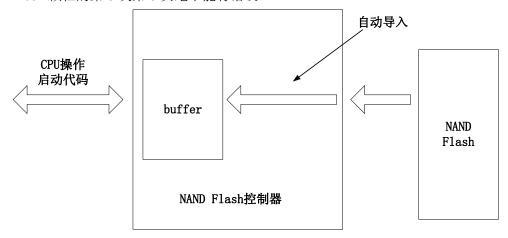

|          | 6.3.8 NAND Flash 启动           |     |

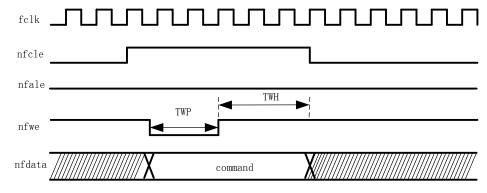

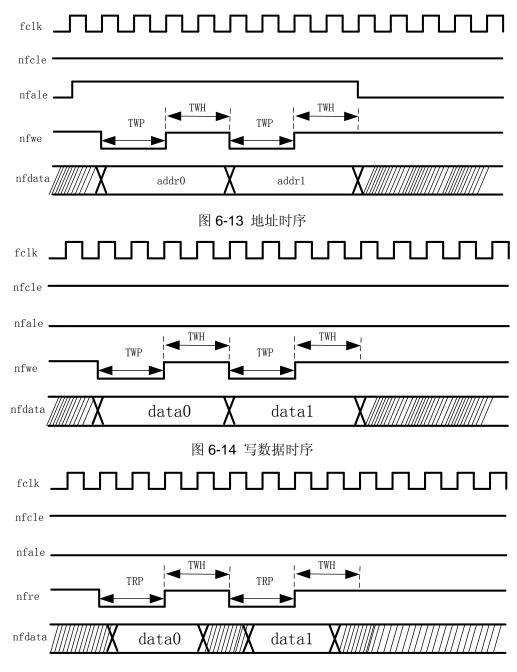

|          | 6.3.9 NAND Flash 接口时序         | 127 |

| 6.4      | 寄存器描述                         | 128 |

| 6.5      | 编程指导                          | 128 |

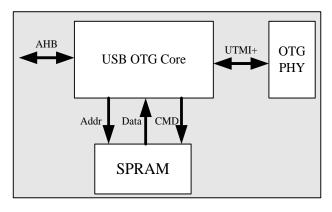

| 7 USB2.0 | ) OTG 控制器                     | 129 |

| 7.1      | 概述                            | 129 |

| 7.2      | 引脚描述                          | 129 |

| 7.3      | 功能说明                          | 130 |

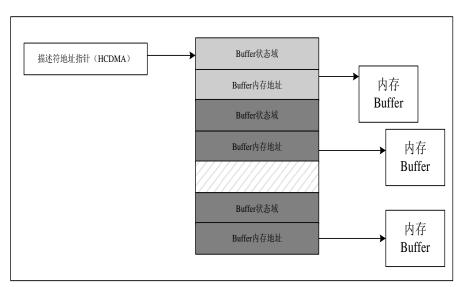

|          | 7.3.1 DMA 模式简介                |     |

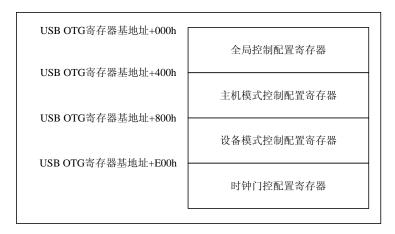

|          | 7.3.2 地址映射                    | 132 |

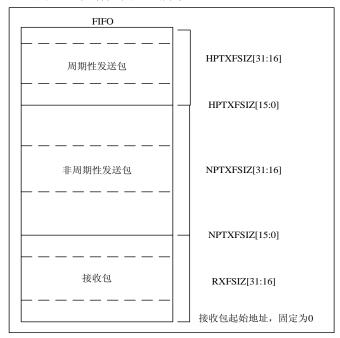

|          | 7.3.3 主机模式                    | 133 |

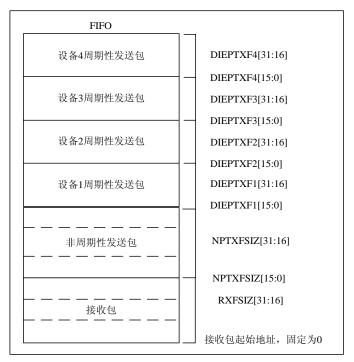

|          | 7.3.4 设备模式                    | 134 |

| 7.4      | 主机/设备工作流程                     | 134 |

|          | 7.4.1 USB OTG 上电初始化           |     |

|          | 7.4.2 主机模式工作流程                |     |

|          | 7.4.3 设备模式工作流程                |     |

|          | 寄存器描述                         |     |

|          | 编程指导                          |     |

|          | 网 MAC 控制器                     |     |

|          | 概述                            |     |

|          | 引脚描述                          |     |

| 8.3      | 功能说明                          |     |

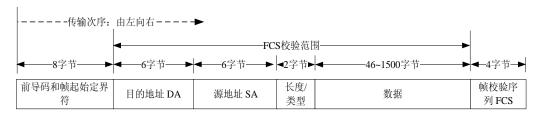

|          | 8.3.1 以太网 MAC 帧格式             |     |

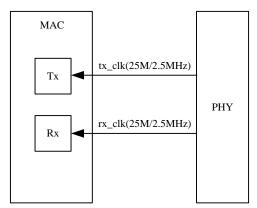

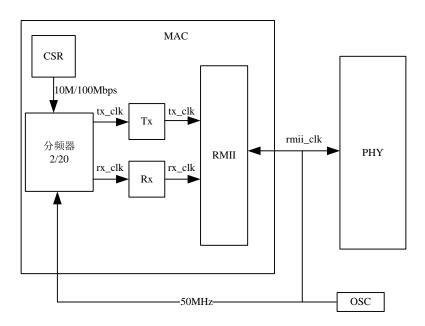

|          | 8.3.2 应用时钟方案                  |     |

|          | 8.3.3 工作模式切换                  |     |

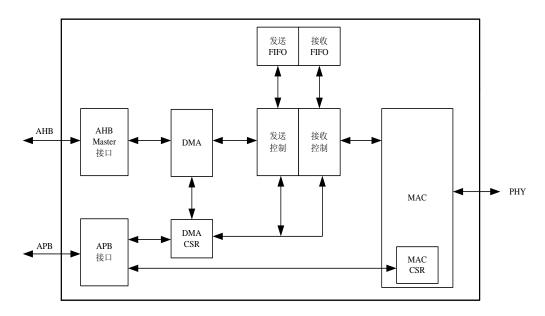

|          | 8.3.4 模块结构与工作原理               |     |

|          | 8.3.4.1 收发过程                  |     |

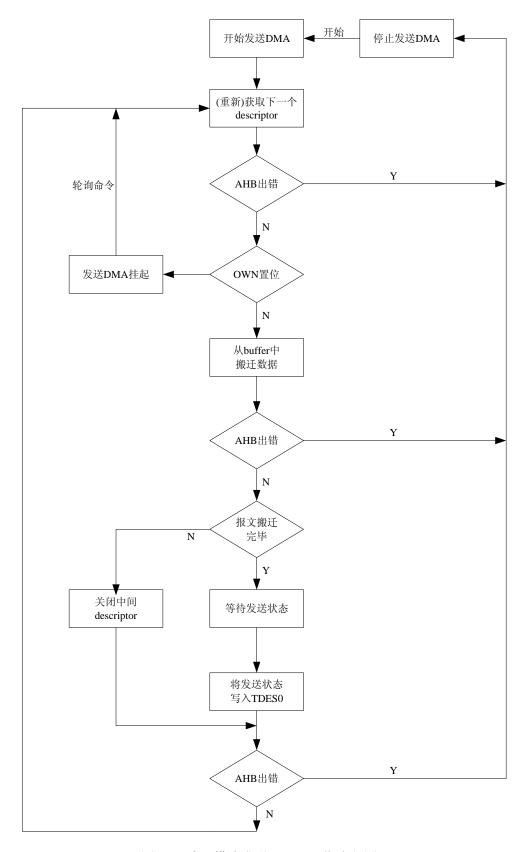

|          | 8.3.4.2 默认模式 DMA 发送过程         |     |

|          | 8.3.4.3 OSF 模式 DMA 发送过程       |     |

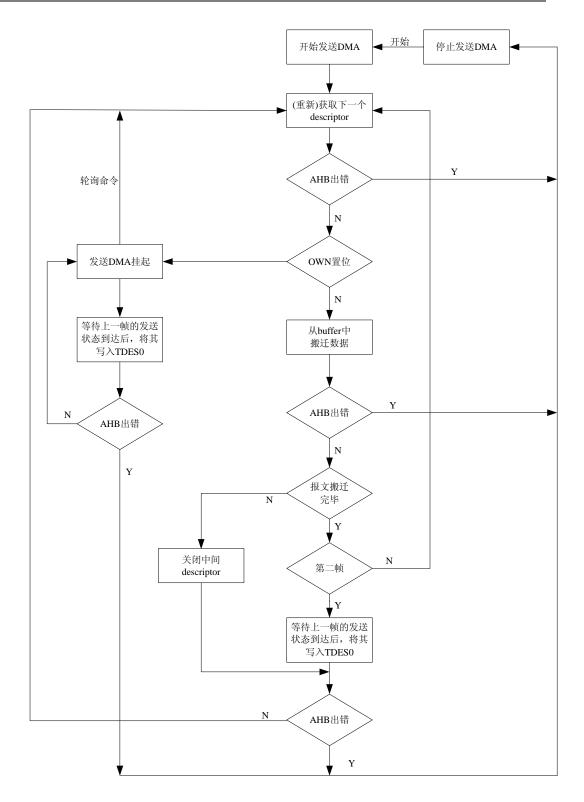

|          | 8.3.4.4 DMA 接收过程              |     |

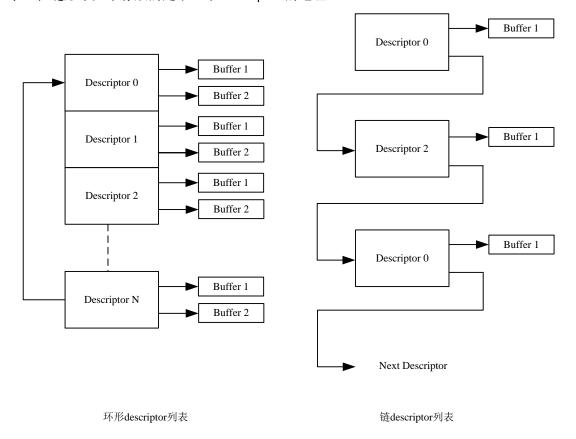

|          | 8.3.5 Descriptor              | 150 |

| 8.3.5.2 接收 Descriptor   |     |

|-------------------------|-----|

|                         | 153 |

| 8.3.7 流控机制              |     |

|                         | 154 |

| 8.3.8 Hash              | 154 |

| 8.3.9 中断与出错             | 155 |

| 8.3.9.1 中断              | 155 |

| 8.3.9.2 出错              | 155 |

| 8.4 寄存器描述               | 156 |

| 8.5 编程指导                | 156 |

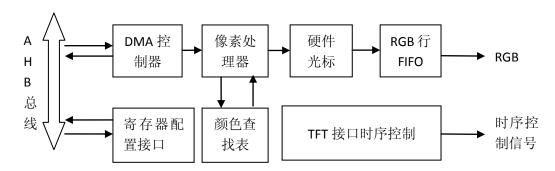

| 9 LCD 控制器               | 157 |

| 9.1 概述                  | 157 |

| 9.2 引脚描述                | 157 |

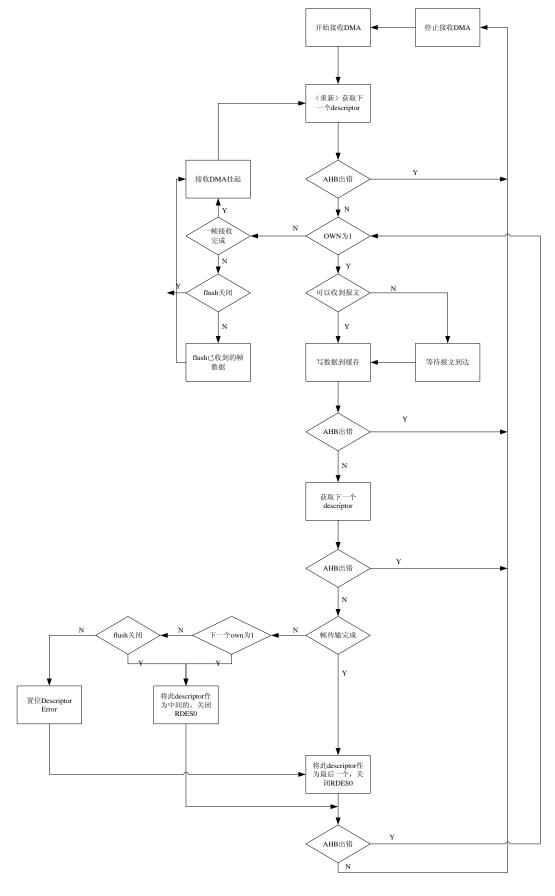

| 9.3 功能说明                | 158 |

| 9.3.1 像素生成原理            | 158 |

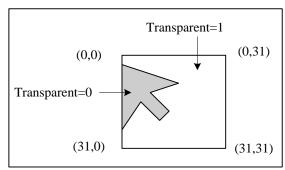

| 9.3.2 硬件光标              | 160 |

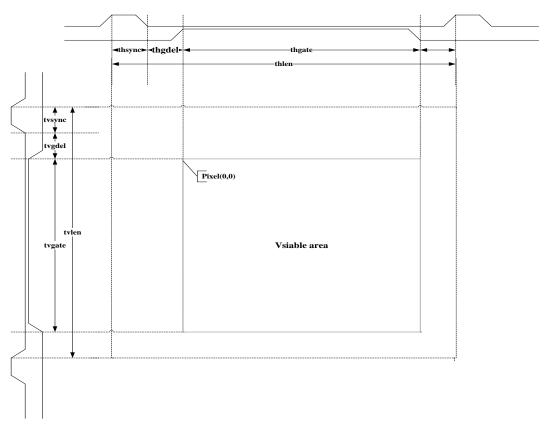

| 9.3.3 LCD 控制器工作时序和刷新率计算 | 160 |

| 9.3.4 DMA 以及访存带宽估算      | 162 |

| 9.4 寄存器描述               | 163 |

| 9.5 编程指导                | 163 |

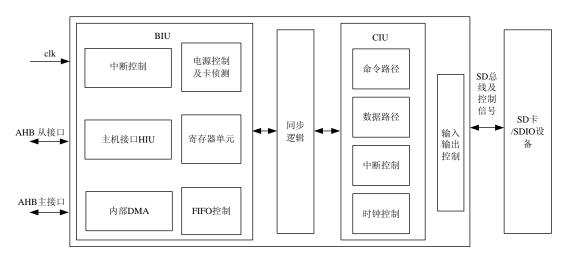

| 10 SD/SDIO 主控制器         | 164 |

| 10.1 概述                 | 164 |

| 10.2 引脚描述               | 164 |

| 10.3 功能说明               | 164 |

| 10.3.1 时钟描述             | 165 |

| 10.3.2 总线接口单元 BIU       | 165 |

| 10.3.3 内部 DMA           | 166 |

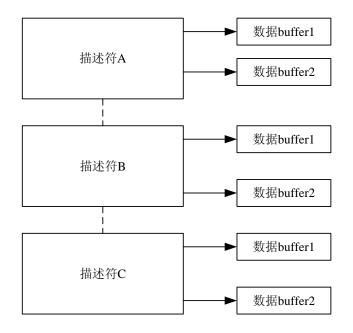

| 10.3.3.1 描述符            | 166 |

| 10.3.3.2 初始化            | 169 |

| 10.3.3.2.1 主机总线的突发访问    | 169 |

| 10.3.3.2.2 计算 Buffer 大小 | 169 |

| 10.3.3.2.3 发送           | 169 |

| 10.3.3.2.4 接收           | 170 |

| 10.3.3.2.5 中断           | 170 |

| 10.3.3.2.6 中止           |     |

| 10.3.3.3 致命总线错误 FBE     | 171 |

| 10.3.4 卡接口单元 CIU        | 171 |

| 10.4 寄存器描述              | 172 |

| 10.5 编程指导               |     |

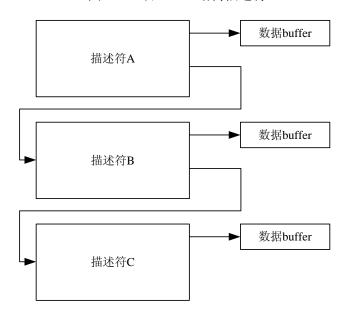

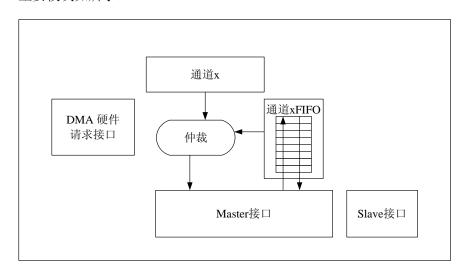

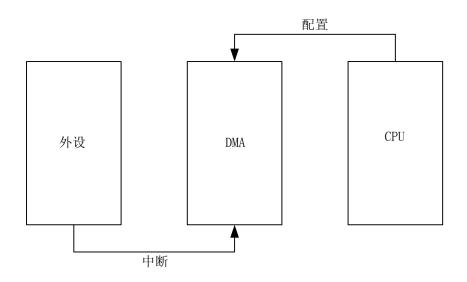

| 11 DMA 控制器              |     |

| 11.1 概述                 |     |

| 11.2 功能说明               |     |

| 11.2.1 DMA 类型           |     |

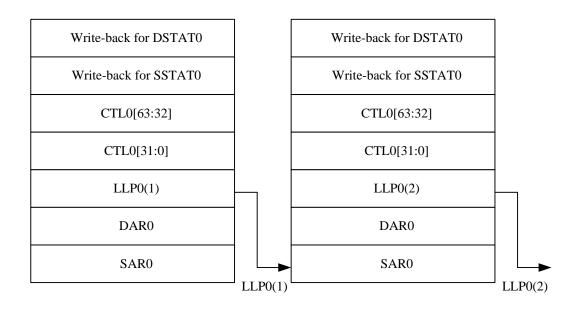

| 11.2.2 链表多块传输           |     |

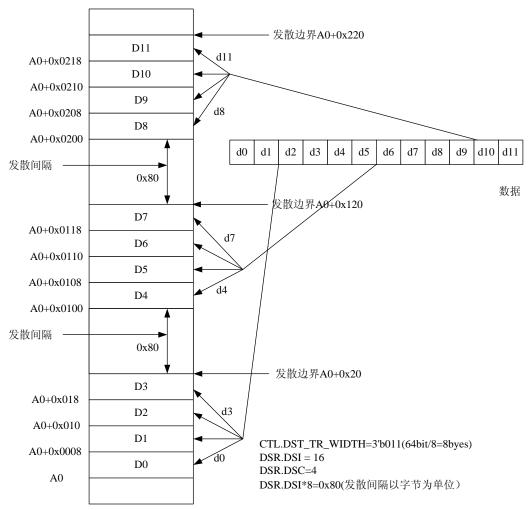

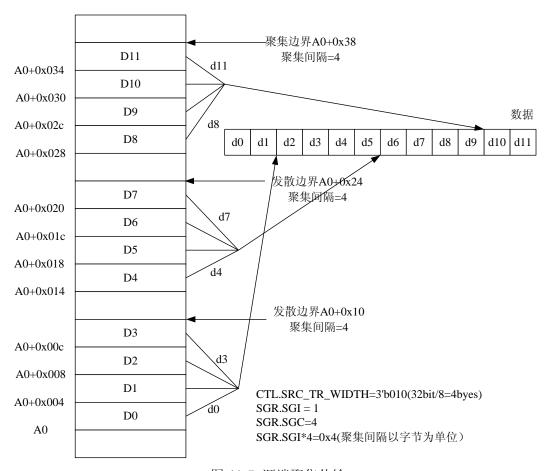

|    |      | 11.2.3 发散和聚集传输                        | 176 |

|----|------|---------------------------------------|-----|

|    |      | 11.2.4 DMA 寄存器访问及非法访问                 | 178 |

|    |      | 11.2.5 DMA 软件握手                       | 178 |

|    |      | 11.2.6 DMA 硬件握手及编号                    | 179 |

|    |      | 11.2.7 DMA FIFO 模式                    | 180 |

|    |      | 11.2.8 DMA 中断                         | 180 |

|    |      | 11.2.9 DMA 的传输类型及流控                   | 181 |

|    |      | 11.2.10 DMA 传输长度及传输宽度                 | 181 |

|    |      | 11.2.11 DMA 传输结束及提前终止                 | 183 |

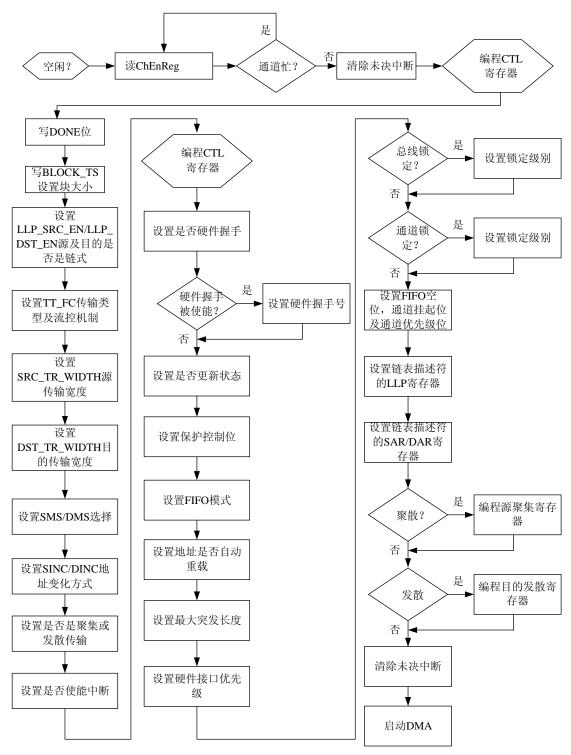

|    |      | 11.2.12 DMA 编程流程                      | 183 |

|    | 11.3 | 寄存器描述                                 | 184 |

|    | 11.4 | 编程指导                                  | 185 |

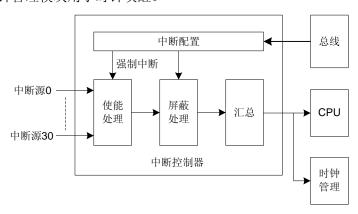

| 12 | 中断打  | 空制器                                   | 186 |

|    | 12.1 | 概述                                    | 186 |

|    | 12.2 | 功能特性                                  | 186 |

|    | 12.3 | 结构框图                                  | 186 |

|    | 12.4 | 功能说明                                  | 187 |

|    |      | 12.4.1 中断源                            | 187 |

|    |      | 12.4.2 中断产生                           | 188 |

|    |      | 12.4.3 强制中断                           | 188 |

|    |      | 12.4.4 中断状态                           | 188 |

|    |      | 12.4.5 中断初始化                          | 189 |

|    |      | 12.4.6 中断处理                           | 189 |

|    | 12.5 | 寄存器描述                                 | 189 |

|    | 12.6 | 编程指导                                  | 189 |

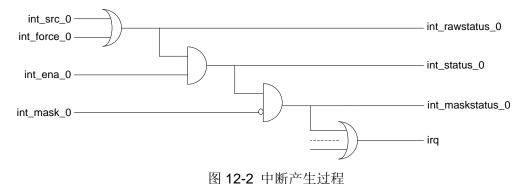

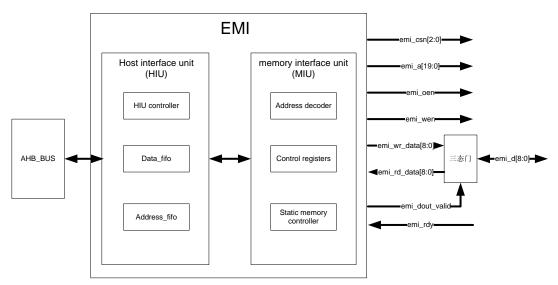

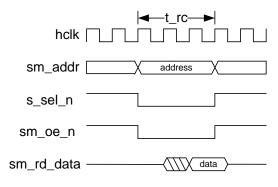

| 13 | 外部情  | 静态存储器接口                               | 190 |

|    | 13.1 | 概述                                    | 190 |

|    | 13.2 | 引脚描述                                  | 190 |

|    | 13.3 | 功能框图                                  | 191 |

|    | 13.4 | 功能说明                                  | 191 |

|    |      | 13.4.1 EMI 接口 NOR Flash 启动            | 191 |

|    |      | 13.4.2 配置片选对应地址                       | 192 |

|    |      | 13.4.3 配置片选对应多地址                      | 192 |

|    |      | 13.4.4 配置外部存储器读写时序参数                  | 192 |

|    |      | 13.4.4.1 异步 SRAM                      | 192 |

|    |      | 13.4.4.2 异步 NOR Flash                 | 192 |

|    |      | 13.4.4.3 读时序                          | 192 |

|    |      | 13.4.4.4 写时序                          | 193 |

|    | 13.5 | 寄存器描述                                 |     |

|    |      | ····································· |     |

| 14 |      | 制器                                    |     |

|    |      | 概述                                    |     |

|    |      | 引脚描述                                  |     |

|    |      | 功能特性                                  |     |

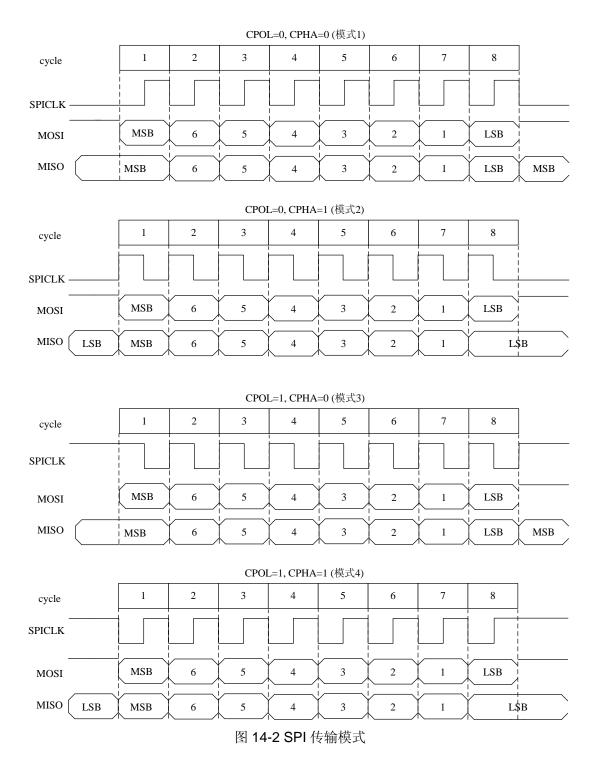

|          | 14.3.1 SPI 传输模式                    | 196 |

|----------|------------------------------------|-----|

|          | 14.3.2 SPI 时钟                      | 197 |

|          | 14.3.3 SPI 中断                      | 198 |

|          | 14.3.4 SPI 控制器编程流程                 | 198 |

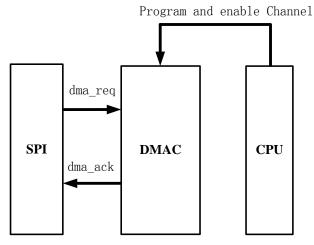

|          | 14.3.5 SPI 的 DMA 操作                | 198 |

|          | 14.3.6 SPI Flash 启动                | 199 |

|          | 14.3.7 SPI 片选                      | 199 |

|          | 14.3.8 SPIO 的触摸屏及 ADC 采样操作         | 200 |

| 14.4     | 寄存器描述                              | 200 |

| 14.5     | 编程指导                               | 201 |

| 15 UART  | 接口                                 | 202 |

| 15.1     | 概述                                 | 202 |

| 15.2     | 引脚描述                               | 202 |

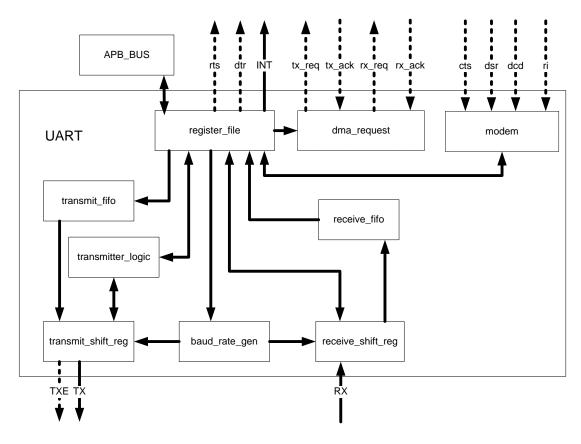

| 15.3     | 功能框图                               | 203 |

| 15.4     | 功能说明                               | 204 |

|          | 15.4.1 波特率计算                       | 204 |

|          | 15.4.2 时钟产生                        | 204 |

|          | 15.4.3 中断与中断屏蔽                     | 205 |

|          | 15.4.4 可编程发送缓冲器空中断                 | 205 |

|          | 15.4.5 DMA 功能                      | 205 |

|          | 15.4.6 自流控功能                       | 205 |

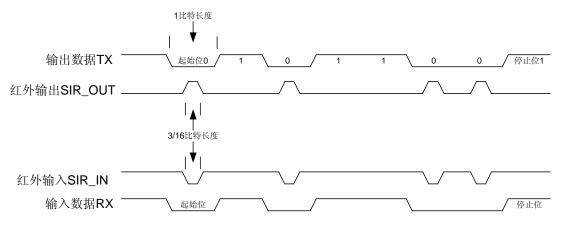

|          | 15.4.7 IRDA 红外功能                   | 206 |

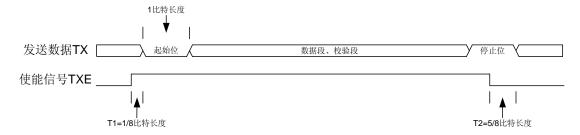

|          | 15.4.8 RS485 输出使能信号 TXE            | 206 |

| 15.5     | 寄存器描述                              | 207 |

| 15.6     | 编程指导                               | 207 |

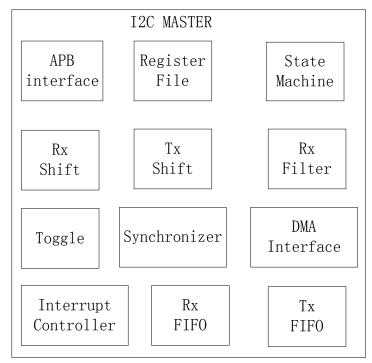

| 16 I2C 控 | 制器                                 | 208 |

| 16.1     | 概述                                 | 208 |

| 16.2     | 引脚描述                               | 208 |

| 16.3     | 功能说明                               | 208 |

|          | 16.3.1 支持协议                        | 208 |

|          | 16.3.2 功能特点                        | 208 |

|          | 16.3.3 功能描述                        | 208 |

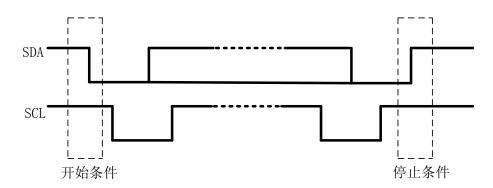

|          | 16.3.4 I2C 时序                      | 209 |

|          | 16.3.4.1 开始和停止条件                   | 209 |

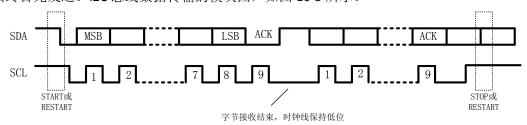

|          | 16.3.4.2 I2C 总线的数据传输               | 210 |

|          | 16.3.5 I2C_CLK 与 SCL               | 210 |

|          | 16.3.5.1 SCL 相关寄存器的最小值             | 210 |

|          | 16.3.5.2 I2C_CLK 的频率最小值            | 211 |

|          |                                    |     |

|          | 16.3.6 两种地址格式                      |     |

|          | 16.3.7 去毛刺                         | 212 |

|          | 16.3.8 SDA 保持时间                    |     |

|          | 16.3.9 FIFO 与 DMA 操作               | 213 |

|          | 16.3.10 发送 FIFO 与 I2C_DATA_CMD 寄存器 | 214 |

| 16.4      | 寄存器描述.        | 2               | 16 |

|-----------|---------------|-----------------|----|

| 16.5      | 编程指导          | 2               | 17 |

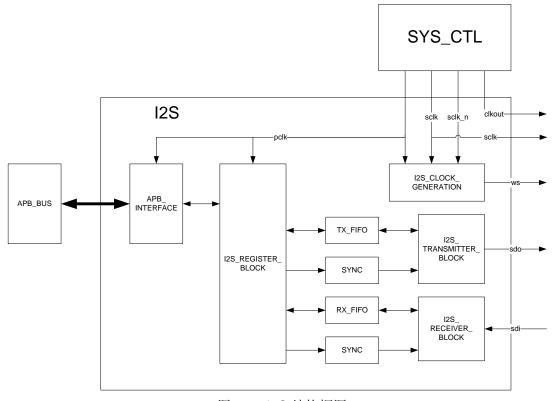

| 17 I2S 控  | 制器            | 2               | 18 |

| 17.1      | 概述            | 2               | 18 |

| 17.2      | 引脚描述          | 2               | 18 |

| 17.3      | 结构框图          | 2               | 18 |

| 17.4      | 功能说明          | 2               | 19 |

|           | 17.4.1 I2S 使能 | <b>尨2</b>       | 19 |

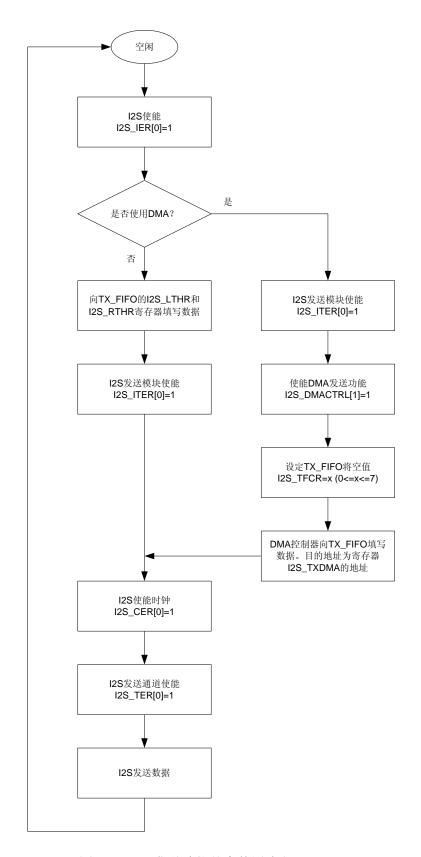

|           | 17.4.2 I2S 发达 | <b>送数据2</b>     | 19 |

|           | 17.4.2.1      | 发送模块使能2         | 21 |

|           | 17.4.2.2      | 发送通道使能2         | 21 |

|           | 17.4.2.3      | 发送音频数据分辨率2      | 21 |

|           | 17.4.2.4      | 发送通道 FIFO2      | 21 |

|           | 17.4.2.5      | 发送通道写数据2        | 22 |

|           | 17.4.2.6      | DMA 发送功能2       | 22 |

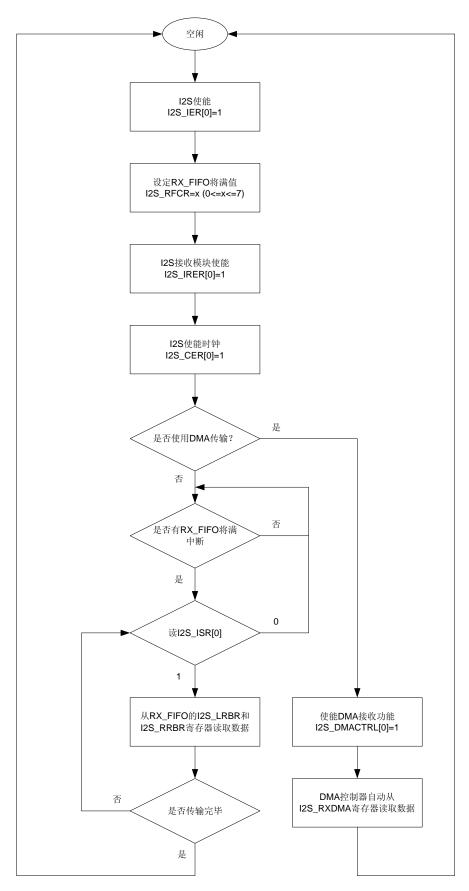

|           | 17.4.3 I2S 接収 | 欠数据2            | 22 |

|           | 17.4.3.1      | 接收模块使能2         | 24 |

|           | 17.4.3.2      | 接收通道使能2         | 24 |

|           | 17.4.3.3      | 接收音频数据分辨率2      | 24 |

|           | 17.4.3.4      | 接收通道 FIFO2      | 24 |

|           | 17.4.3.5      | 接收通道读数据2        | 25 |

|           | 17.4.3.6      | DMA 接收功能2       | 25 |

|           | 17.4.4 中断与    | <b>5中断屏蔽2</b>   | 25 |

|           | 17.4.5 时钟产    | <sup></sup> 生2  | 26 |

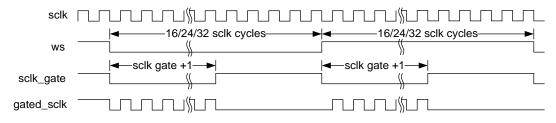

|           | 17.4.5.1      | clkout 产生2      | 26 |

|           | 17.4.5.2      | sclk 产生2        | 26 |

|           | 17.4.5.3      | word select 产生2 | 26 |

|           | 17.4.5.4      | 时钟配置示例2         | 27 |

| 17.5      | 寄存器描述.        | 2               | 27 |

| 17.6      | 编程指导          | 2               | 27 |

| 18 PS2 控  | 制器            | 2               | 28 |

| 18.1      | 概述            | 2               | 28 |

| 18.2      | 引脚描述          | 2               | 28 |

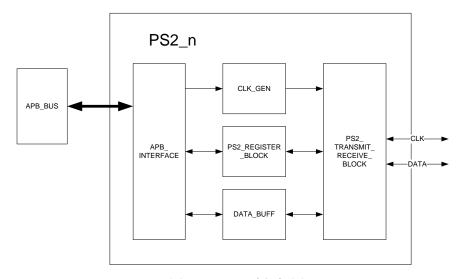

| 18.3      | 功能框图          | 2               | 28 |

| 18.4      | 功能说明          | 2               | 29 |

|           |               | 产生2             |    |

|           | 18.4.2 中断与    | 5中断使能2          | 29 |

|           | -             | 7令字2            |    |

|           |               | 示和分频寄存器设置2      |    |

|           |               | 2               |    |

|           |               | 2               |    |

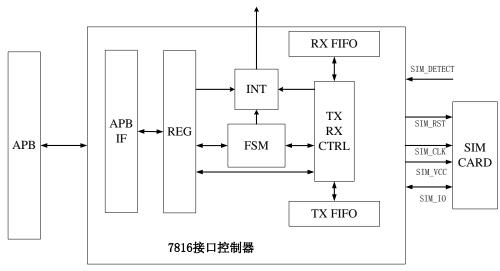

| 19 7816 🖠 | 空制器           | 2               | 32 |

| 19.1      | 概述            | 2               | 32 |

| 19.2      | 引脚描述          | 2               | 32 |

|      | 19.3 | 功能说明                          | .232 |

|------|------|-------------------------------|------|

|      |      | 19.3.1 功能特点                   | .232 |

|      |      | 19.3.2 功能说明                   | .233 |

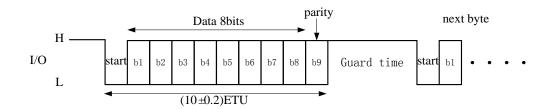

|      |      | 19.3.3 字符帧                    | .233 |

|      |      | 19.3.4 波特率                    | .234 |

|      |      | 19.3.5 保护间隔                   | .234 |

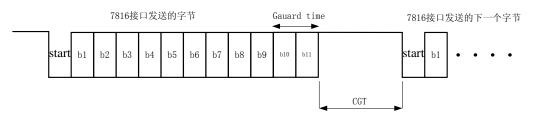

|      |      | 19.3.6 字符间额外保护时间(CGT)         | .234 |

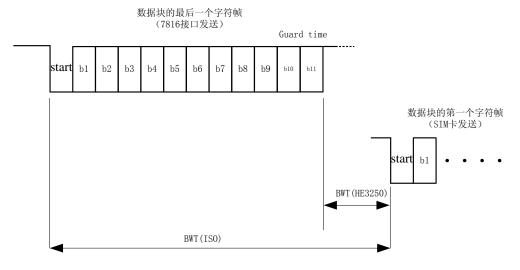

|      |      | 19.3.7 块等待时间(BWT)             | .234 |

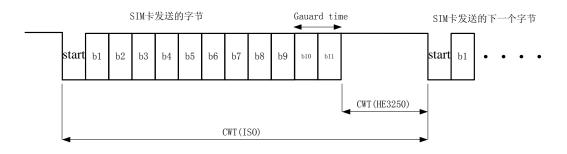

|      |      | 19.3.8 字符间等待时间(CWT)           | .235 |

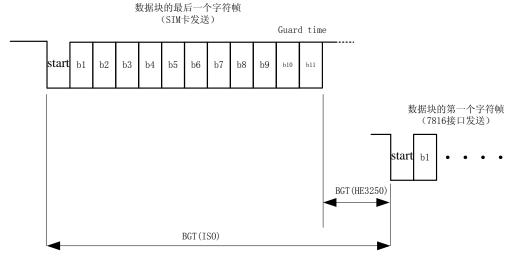

|      |      | 19.3.9 块保护时间(BGT)             | .235 |

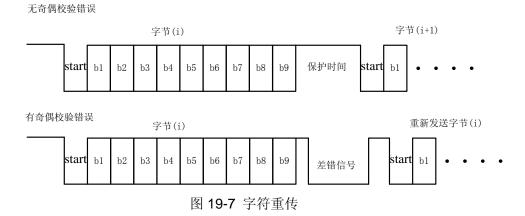

|      |      | 19.3.10 差错信号与字符重传             |      |

|      |      | 19.3.11 FIFO 操作               |      |

|      |      | 19.3.12 SIM 卡的热插拔             |      |

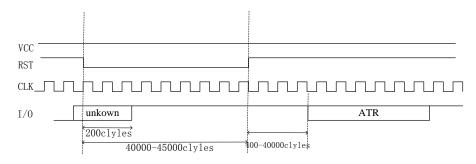

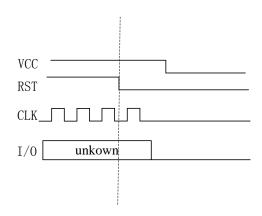

|      |      | 19.3.13 7816 的接口时序            | .237 |

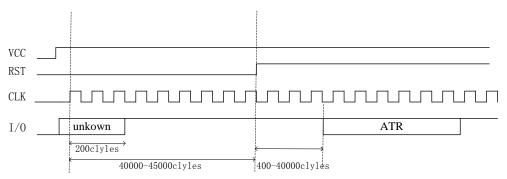

|      |      | 19.3.14 复位应答                  |      |

|      | 19.4 | 寄存器描述                         | .239 |

|      | 19.5 | 编程指导                          | .239 |

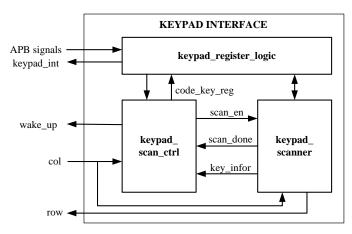

| 20   |      | 建盘接口                          |      |

|      | 20.1 | 概述                            | .240 |

|      |      | 引脚描述                          |      |

|      |      | 功能与原理说明                       |      |

|      |      | 寄存器描述                         |      |

|      |      | 编程指导                          |      |

| 21 ( |      | 2制器                           |      |

|      |      | 概述                            |      |

|      |      | 引脚描述                          |      |

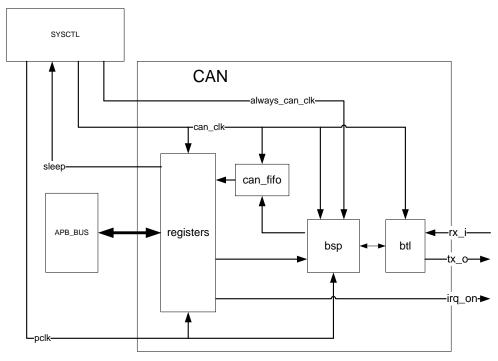

|      |      | 结构框图                          |      |

|      |      | 功能描述                          |      |

|      |      | 21.4.1 接收和发送数据                |      |

|      |      | 21.4.2 时钟描述                   |      |

|      |      | 21.4.3 工作模式与复位模式              |      |

|      |      | 21.4.4 波特率设置与同步               |      |

|      |      | 21.4.5 中断屏蔽与中断清除              |      |

|      |      | 21.4.6 控制器自检测功能               |      |

|      |      | 21.4.7 控制器只听功能                |      |

|      |      | 21.4.8 睡眠与唤醒功能                |      |

|      |      | 21.4.9 错误处理                   |      |

|      |      | 21.4.9.1 错误状态                 |      |

|      |      | 21.4.9.2 错误计数值                |      |

|      |      | 21.4.10 帧的验收数据过滤与验收过滤掩码       |      |

|      |      | 21.4.10.1 单过滤模式               |      |

|      |      | <b>21.4.10.1.1</b> 单过滤模式接收标准帧 |      |

|      |      | 21.4.10.1.2 单过滤模式接收扩展帧        |      |

|      |      | 21.4.10.2 双过滤模式               | .251 |

| 21.4.10.2.1 双过滤模式接收标准帧 | 252 |

|------------------------|-----|

| 21.4.10.2.2 双过滤模式接收扩展帧 | 252 |

| 21.5 仲裁丢失              | 253 |

| 21.6 寄存器描述             | 254 |

| 21.7 编程指导              | 254 |

| 22 ADC 与触摸屏控制器         | 255 |

| 22.1 概述                | 255 |

| 22.2 引脚描述              | 255 |

| 22.3 功能特性              | 255 |

| 22.3.1 触摸屏及 ADC 操作     | 256 |

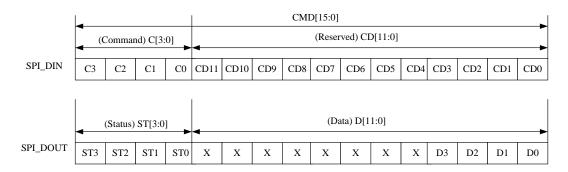

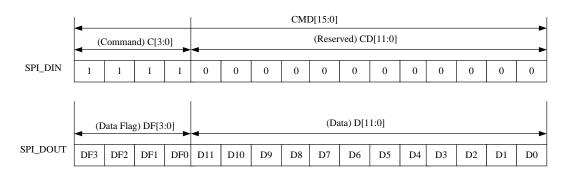

| 22.3.2 命令周期            | 257 |

| 22.3.3 数据周期            | 257 |

| 22.4 时钟及采样率            | 258 |

| 22.5 ADC 自动采样          | 258 |

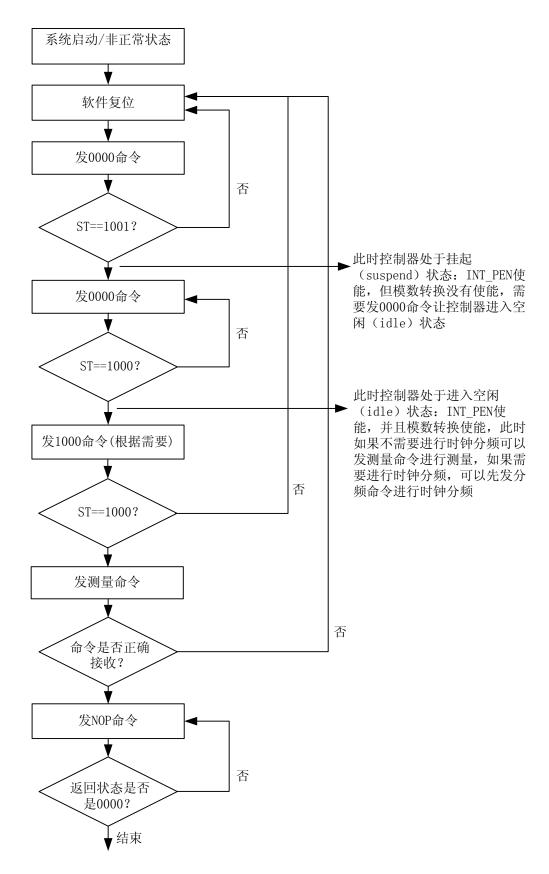

| 22.6 软件操作流程            | 258 |

| 22.7 控制器命令             | 260 |

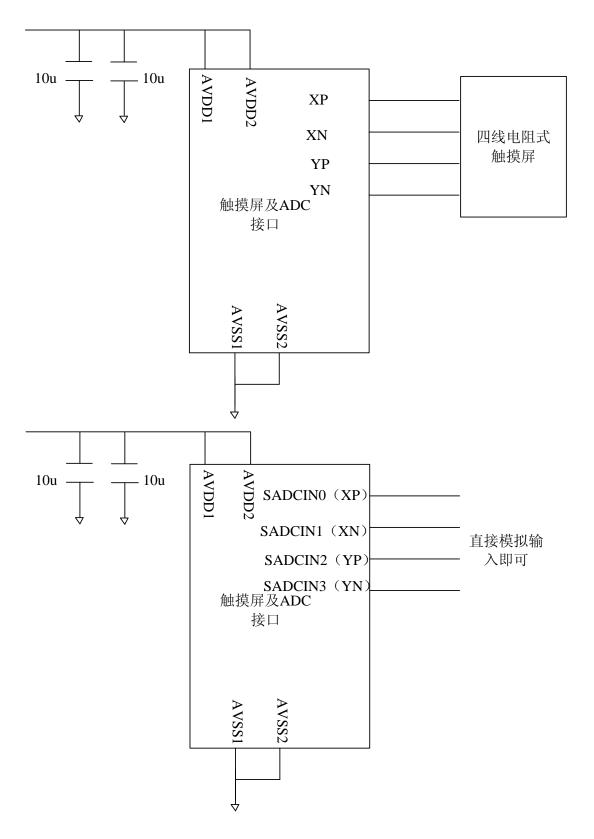

| 22.8 典型应用              | 261 |

| 22.9 编程指导              | 262 |

| 23 PWM 与旋转编码器接口        | 263 |

| 23.1 概述                | 263 |

| 23.2 引脚描述              | 263 |

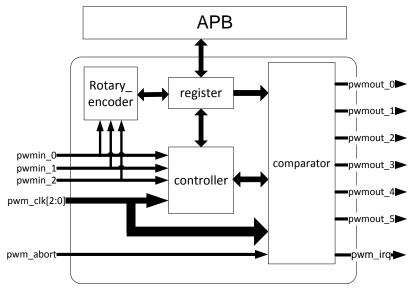

| 23.3 功能框图              | 264 |

| 23.4 功能说明              | 264 |

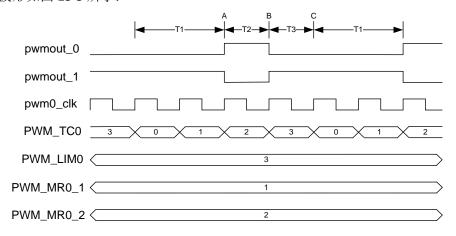

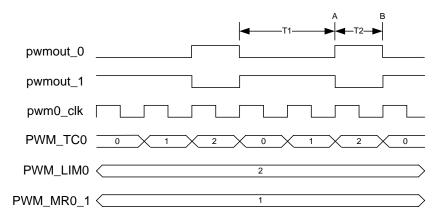

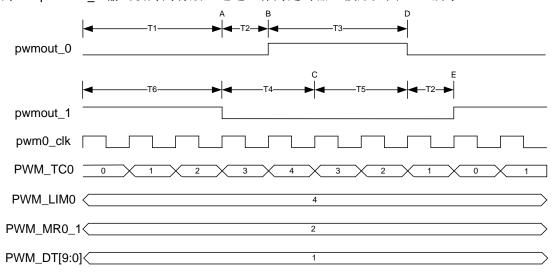

| 23.4.1 PWM 模式          | 264 |

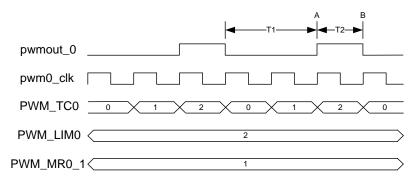

| 23.4.1.1 单边沿模式         | 265 |

| 23.4.1.2 双边沿模式         | 265 |

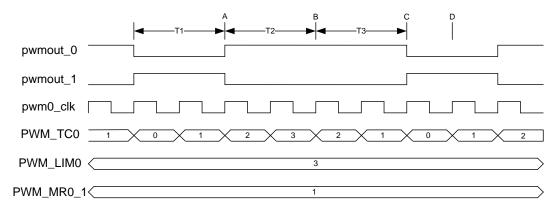

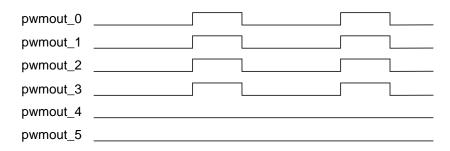

| 23.4.2 MCPWM 模式        | 266 |

| 23.4.2.1 边沿对齐模式        | 266 |

| 23.4.2.2 中心对齐模式        | 267 |

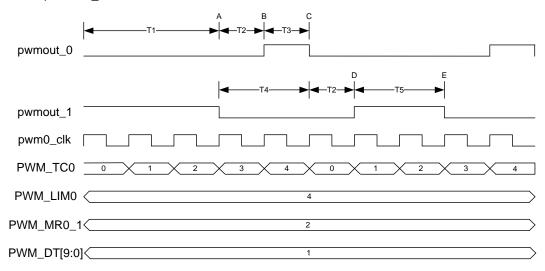

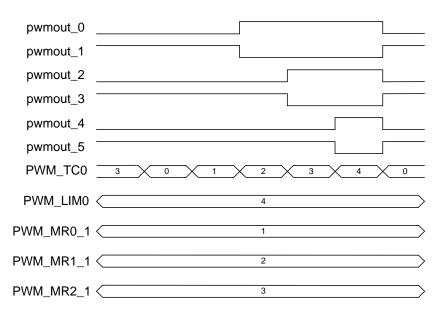

| 23.4.2.3 死区模式          | 268 |

| 23.4.2.3.1 边沿对齐死区模式    | 269 |

| 23.4.2.3.2 中心对齐死区模式    | 269 |

| 23.4.2.4 三相 DC 模式      | 270 |

| 23.4.2.5 三相 AC 模式      | 271 |

| 23.4.3 定时器模式与计数器模式     | 271 |

| 23.4.4 增量式旋转编码器鉴相模块    | 272 |

| 23.4.5 中断与中断屏蔽         | 272 |

| 23.4.6 时钟产生            | 273 |

| 23.5 寄存器描述             | 273 |

| 23.6 编程指导              | 273 |

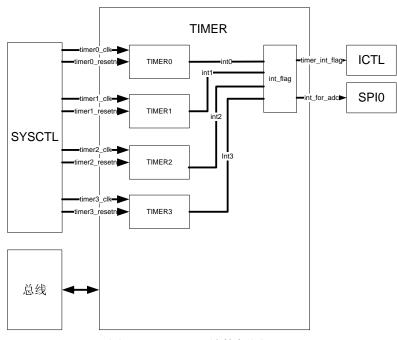

| 24 可编程定时器              | 274 |

| 24.1 概述                | 274 |

| 24.2 结构框图              | 274 |

| 24.3 功能描述              | 274 |

|    | 24.3.1 使能与禁止            | 275 |

|----|-------------------------|-----|

|    | 24.3.2 定时器重载            | 275 |

|    | 24.3.3 中断屏蔽与中断清除        | 275 |

|    | 24.3.4 工作模式             | 276 |

|    | 24.3.4.1 循环定时模式         | 276 |

|    | 24.3.4.2 单次定时模式         | 276 |

|    | 24.4 寄存器描述              | 276 |

|    | 24.5 编程指导               | 276 |

|    | 24.5.1 TIMER 中断状态查询     | 276 |

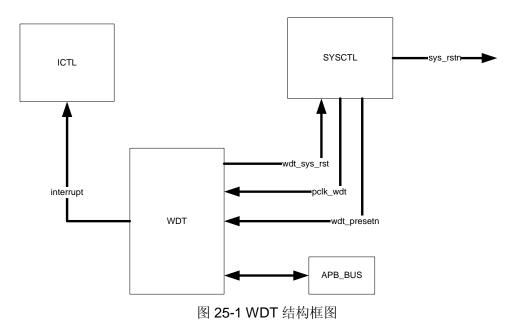

| 25 | 看门狗定时器                  | 278 |

|    | 25.1 概述                 | 278 |

|    | 25.2 结构框图               | 278 |

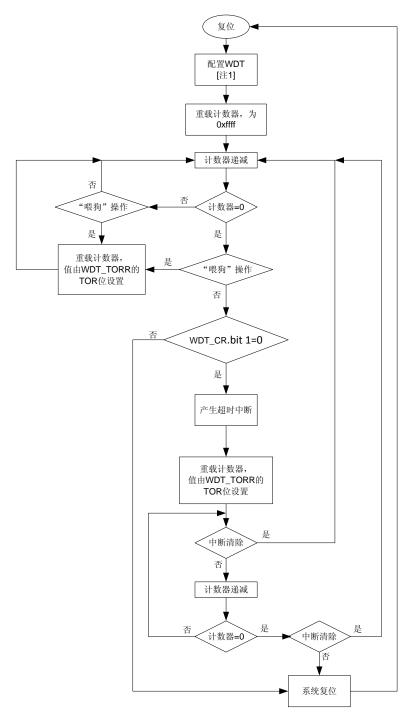

|    | 25.3 功能描述               | 278 |

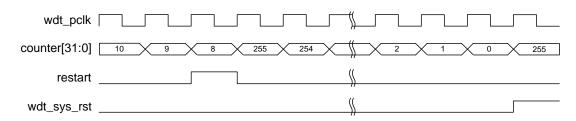

|    | 25.3.1 计数器              | 279 |

|    | 25.3.2 中断与中断清除          | 279 |

|    | 25.3.3 暂停               | 279 |

|    | 25.3.4 生成复位信号           | 279 |

|    | 25.3.5 CPU 等待模式下 WDT 使能 | 280 |

|    | 25.4 WDT 工作流程图          | 281 |

|    | 25.5 寄存器描述              | 281 |

|    | 25.6 编程指导               | 282 |

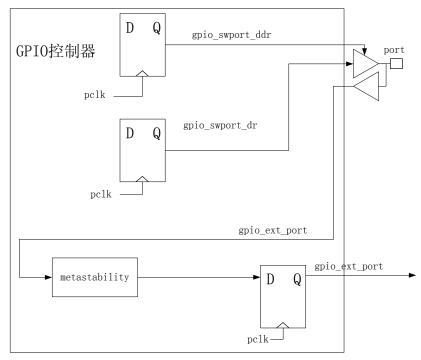

| 26 | 可编程输入输出接口               | 283 |

|    | 26.1 概述                 | 283 |

|    | 26.2 功能说明               | 285 |

|    | 26.2.1 功能特点             | 285 |

|    | 26.2.2 功能描述             | 285 |

|    | 26.2.3 中断               | 286 |

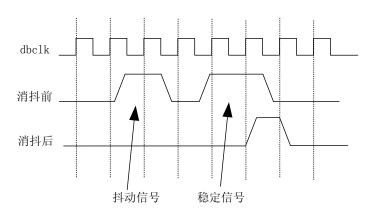

|    | 26.2.4 消抖功能             | 286 |

|    | 26.3 寄存器描述              | 287 |

|    | 26.4 编程指导               | 287 |

| 27 | 订购信息                    | 288 |

| 28 | 修订历史                    | 289 |

# 图目录

| 图 1-1 GSC3280 结构框图            | 5  |

|-------------------------------|----|

| 图 2-1 龙芯处理器逻辑地址空间与物理地址空间的映射关系 | 6  |

| 图 3-1 32 位龙芯结构框图              | 10 |

| 图 3-2 32 位龙芯处理器的逻辑地址空间与地址段划分  | 12 |

| 图 3-3 用户模式下的地址空间              | 13 |

| 图 3-4 监管模式下的地址空间              | 14 |

| 图 3-5 内核模式下的地址空间              | 15 |

| 图 3-6 调试模式下的地址空间              |    |

| 图 3-7 TLB 表项格式                |    |

| 图 3-8 虚实地址转换过程                | 19 |

| 图 3-9 龙芯处理器 32 位虚实地址转换过程图示    | 20 |

| 图 3-10 TLB 虚实地址转换流程           |    |

| 图 3-11 四路组相联 cache 组织结构       |    |

| 图 3-12 指令 cache 块的组成          |    |

| 图 3-13 数据 cache 块的组成          |    |

| 图 3-14 cache 访问过程             |    |

| 图 3-15 TLB 中的固定与随机表项          |    |

| 图 3-16 龙芯处理器指令格式              |    |

| 图 4-1 系统控制模块结构框图              |    |

| 图 4-2 GSC3280 芯片时钟结构概览        |    |

| 图 4-3 PLL 结构框图                |    |

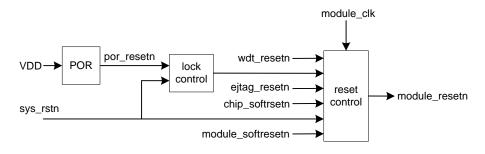

| 图 4-4 GSC3280 复位方案            |    |

| 图 4-5 GSC3280 的休眠模式转换图        |    |

| 图 5-1 DDR2 控制器结构框图            |    |

| 图 5-2 控制器的操作状态机               |    |

| 图 5-3 DDR2 PHY 上电复位序列         |    |

| 图 5-4 DFI 控制信号时间参数            |    |

| 图 5-5 DFI 写操作时间参数             |    |

| 图 5-6 DFI 读操作时间参数             |    |

| 图 6-1 NAND Flash 控制器结构        |    |

| 图 6-2 内置 BUFFER               |    |

| 图 6-3 BUFFER 与寄存器的地址映射关系      |    |

| 图 6-4 DMA 整页写操作               |    |

| 图 6.5 DMA 整页读操作               |    |

| 图 6-6 整页读操作                   |    |

| 图 6-7 普通读操作                   |    |

| 图 6-8 整页写操作                   |    |

| 图 6-9 普通写操作                   |    |

| 图 6-10 块擦除操作                  |    |

| 图 6-11 NAND Flash 启动          |    |

| 181 M 17 101 7 HTTT           |    |

| 冬 | 6-13 地址时序                           | .128 |

|---|-------------------------------------|------|

| 冬 | 6-14 写数据时序                          | .128 |

| 冬 | 6-15 读数据时序                          | .128 |

| 冬 | 7-1 USB OTG 控制器结构图                  | .130 |

| 冬 | 7-2 描述符表                            | .130 |

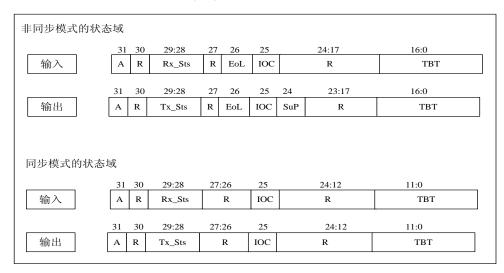

| 图 | 7-3 Scatter Gather 模式下 Buffer 状态域定义 | .131 |

| 图 | 7-4 寄存器地址映射                         | .132 |

| 冬 | 7-5 主机模式下 FIFO 地址映射                 | .132 |

|   | 7-6 设备模式下 FIFO 地址映射                 |      |

|   | 9-1 LCD 控制器工作原理                     |      |

|   | 9-2 LCD 控制器模块总体架构                   |      |

| 冬 | 9-3 16bpp 模式内存数据与像素数据对应关系           | 159  |

|   | 9-4 8bpp 模式内存数据与像素数据对应关系            |      |

|   | 9-5 8bpp 模式查找表格式                    |      |

|   | 9-6 硬件光标像素定义图示                      |      |

|   | 9-7 硬件光标像素数据格式                      |      |

|   | 9-8 LCD 控制器时序                       |      |

|   | 10-1 SD/SDIO 主控制器框图                 |      |

|   | 10-2 双 buffer 结构描述符                 |      |

|   | 10-3 链式结构描述符                        |      |

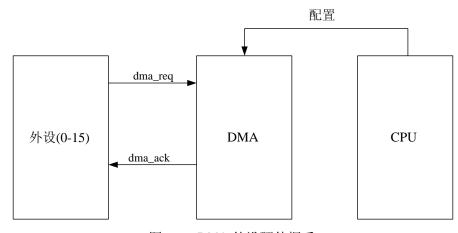

|   | 11-1 DMA 框图                         |      |

|   | 11-2 DMA 与相关外设连接图                   |      |

|   | 11-3 链表描述符                          |      |

|   | 11-4 目的端发散传输                        |      |

|   | 11-5 源端聚集传输                         |      |

|   | 11-6 DMA 外设软件握手                     |      |

|   | 11-7 DMA 外设硬件握手                     |      |

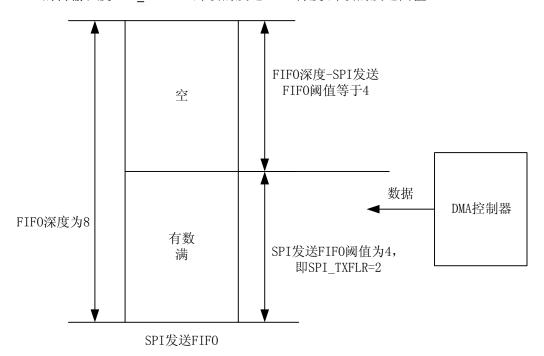

|   | 11-8 DMA DST_MSIZE 和外设 FIFO 设置      |      |

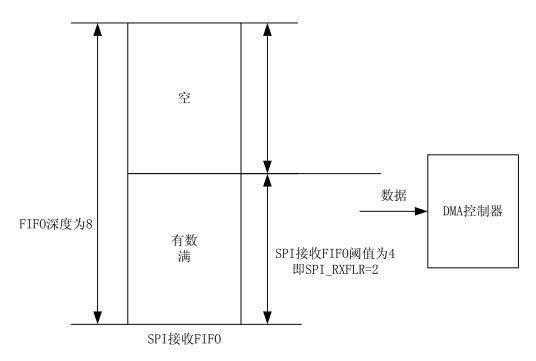

|   | 11-9 DMA SRC_MSIZE 和外设 FIFO 设置      |      |

|   | 11-10 DMA 编程流程                      |      |

|   | 12-1 中断控制器结构框图                      |      |

|   | 12-2 中断产生过程                         |      |

|   | 13-1 EMI 功能框图                       |      |

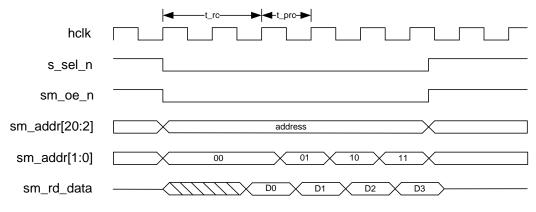

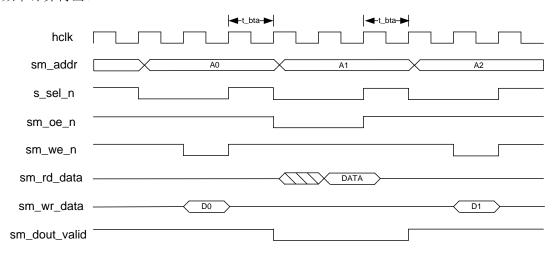

|   | 13-2 SRAM/NOR Flash 读周期时序           |      |

|   | 13-3 SRAM/NOR Flash 页模式读周期时序        |      |

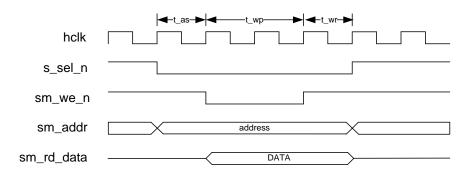

|   | 13-4 SRAM/NOR Flash 写周期时序           |      |

|   | 13-5 SRAM/NOR Flash 读写间隔时序          |      |

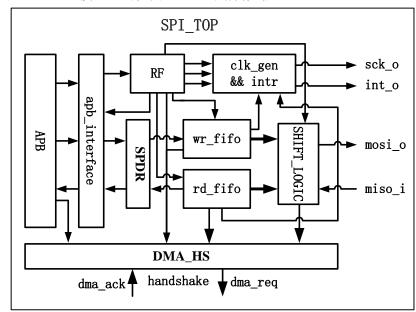

|   | 14-1 SPI 框图                         |      |

|   | 14-2 SPI 传输模式                       |      |

|   | 14-3 SPI DMA 接口示意图                  |      |

|   | 15-1 UART 功能框图                      |      |

|   | 15-2 红外发送和接收数据格式                    |      |

|   | 15-3 输出使能信号 TXE 时序图                 |      |

| 冬 | 16-1 I2C MASTER 结构                  | .209 |

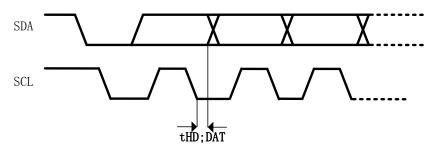

| 图 16-2 开始和停止条件                                | 210 |

|-----------------------------------------------|-----|

| 图 16-3 I2C 总线数据传输                             | 210 |

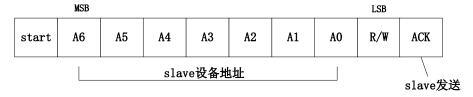

| 图 16-4 7bit 地址格式                              | 212 |

| 图 16-5 10bit 地址格式                             | 212 |

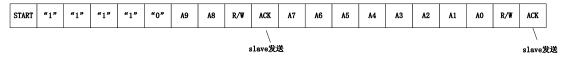

| 图 16-6 去毛刺示意图                                 | 213 |

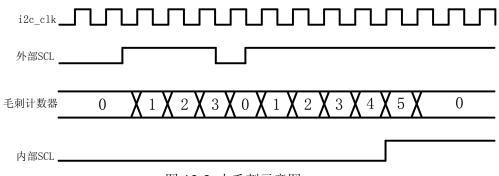

| 图 16-7 SDA 保持时间                               | 213 |

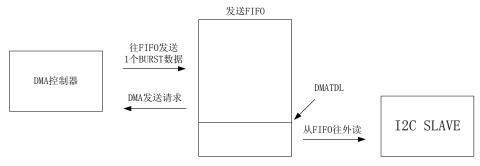

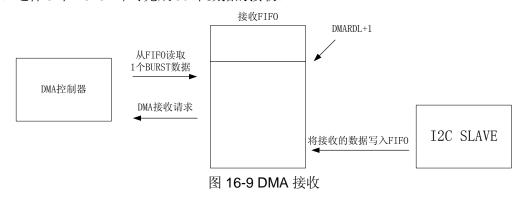

| 图 16-8 DMA 发送                                 | 214 |

| 图 16-9 DMA 接收                                 | 214 |

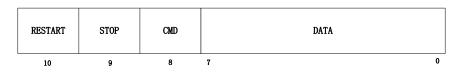

| 图 16-10 I2C_DATA_CMD 寄存器                      | 214 |

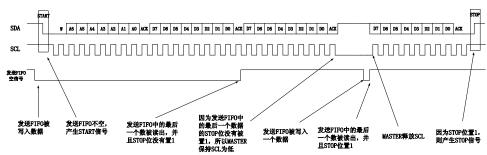

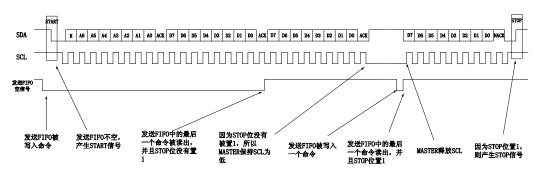

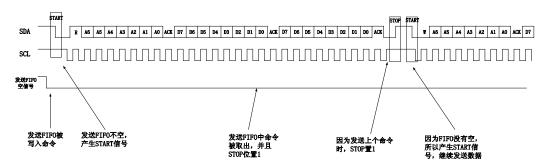

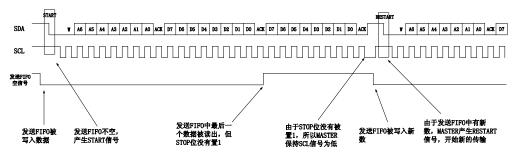

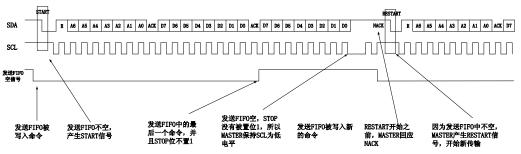

| 图 16-11 发送状态下,发送 FIFO 变空并且 STOP 位置 1 的时序图     | 215 |

| 图 16-12 接收状态下,发送 FIFO 变空并且 STOP 位置 1 的时序图     | 215 |

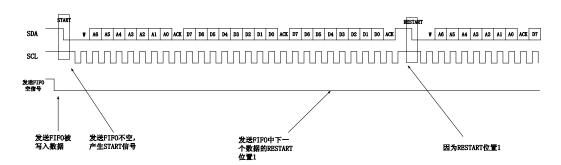

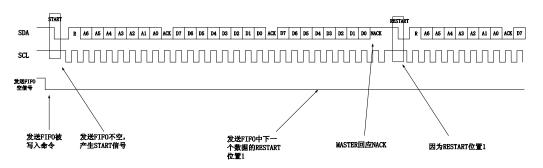

| 图 16-13 发送状态下,发送 FIFO 非空时并且 RESTART 位置 1 的时序图 | 215 |

| 图 16-14 接收状态下,发送 FIFO 非空时并且 RESTART 位置 1 的时序图 | 215 |

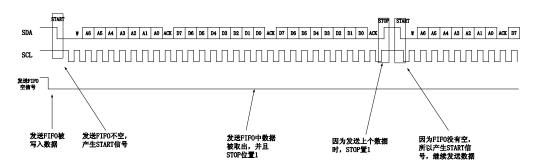

| 图 16-15 发送状态下,发送 FIFO 非空时并且 STOP 位置 1 的时序图    | 216 |

| 图 16-16 接收状态下,发送 FIFO 非空时并且 STOP 位置 1 的时序图    | 216 |

| 图 16-17 发送状态下,发送 FIFO 由空变非空时产生 RESTART 信号的时序图 | 216 |

| 图 16-18 接收状态下,发送 FIFO 由空变非空时产生 RESTART 信号的时序图 | 216 |

| 图 17-1 I2S 结构框图                               | 218 |

| 图 17-2 I2S 发送功能基本使用流程                         | 220 |

| 图 17-3 I2S 接收功能基本使用流程                         | 223 |

| 图 17-4 I2S sclk 门控信号波形示意图                     | 226 |

| 图 18-1 PS2 功能框图                               | 229 |

| 图 19-1 7816 接口总体架构                            | 233 |

| 图 19-2 字符帧结构                                  | 233 |

| 图 19-3 字符间额外保护时间                              | 234 |

| 图 19-4 块保护时间                                  | 235 |

| 图 19-5 字符间等待时间                                | 235 |

| 图 19-6 块保护时间                                  | 236 |

| 图 19-7 字符重传                                   | 237 |

| 图 19-8 SIM 卡的冷复位时序                            | 238 |

| 图 19-9 SIM 卡热复位时序                             | 238 |

| 图 19-10 SIM 卡释放时序                             | 239 |

| 图 21-1 CAN 控制器结构框图                            | 244 |

| 图 21-2 标准数据帧格式                                | 245 |

| 图 21-3 扩展数据帧格式                                | 245 |

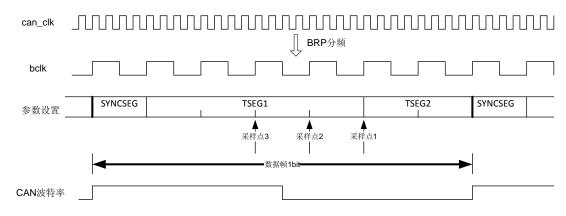

| 图 21-4 CAN 波特率示意图                             | 246 |

| 图 22-1 触摸屏及 ADC 命令周期                          | 257 |

| 图 22-2 触摸屏及 ADC 数据周期                          | 258 |

| 图 22-3 ADC 与触摸屏控制器操作流程图                       | 259 |

| 图 22-4 ADC 与触摸屏控制器典型应用                        | 261 |

| 图 23-1 PWM 功能框图                               | 264 |

| 图 23-2 PWM 模式单边沿输出示意图                         |     |

| 图 23-3 PWM 模式双边沿输出示意图                         | 266 |

| 图 23-4 MCPWM 模式边沿对齐输出示意图                      |     |

| 图 23-5 MCPWM 模式中心对齐输出示意图     | 268 |

|------------------------------|-----|

| 图 23-6 MCPWM 模式边沿对齐死区模式输出示意图 | 269 |

| 图 23-7 MCPWM 模式中心对齐死区模式输出示意图 | 270 |

| 图 23-8 三相 DC 模式输出示意图         | 271 |

| 图 23-9 三相 AC 模式输出示意图         | 271 |

| 图 24-1 TIMER 结构框图            | 274 |

| 图 25-1 WDT 结构框图              | 278 |

| 图 25-2 WDT 计数器复位和系统复位信号时序图   | 280 |

| 图 25-3 WDT 工作流程图             | 281 |

| 图 26-1 GPIO 控制器结构图           | 286 |

| 图 26-2 消抖时序图                 | 287 |

|                              |     |

# 表目录

| 表 2-1 GSC3280 芯片的存储器地址映射表         | 7   |

|-----------------------------------|-----|

| 表 3-1 用户模式下地址段属性                  | 13  |

| 表 3-2 监管模式下地址段属性                  | 14  |

| 表 3-3 内核模式下地址段属性                  | 15  |

| 表 3-4 dseg 地址段的划分与属性              |     |

| 表 3-5 drseg 地址段的访问                | 17  |

| 表 3-6 dmseg 地址段的访问                | 17  |

| 表 3-7 TLB 表项位域说明                  |     |

| 表 3-8 龙芯处理器的 cache 指令操作           |     |

| 表 3-9 龙芯处理器例外优先级                  |     |

| 表 3-10 龙芯处理器例外入口的向量基址             |     |

| 表 3-11 龙芯处理器例外入口的向量偏移量            |     |

| 表 3-12 龙芯处理器的 CPO 寄存器列表           |     |

| 表 3-13 Cause 寄存器 ExcCode 域描述      |     |

| 表 3-14 数据存取指令描述使用到的描述性函数          |     |

| 表 3-15 龙芯处理器指令集汇总                 |     |

| 表 4-1 GSC3280 启动模式配置              |     |

| 表 4-2 GSC3280 芯片时钟概览              |     |

| 表 4-3 GSC3280 芯片时钟配置引脚对 PLL 的配置情况 |     |

| 表 5-1 DDR2 控制器引脚描述                |     |

| 表 5-2 XPI 中的队列深度                  |     |

| 表 5-3 命令的优先级                      |     |

| 表 5-4 与 JEDEC 兼容的内存颗粒地址位宽         |     |

| 表 5-5 系统地址到内存地址的映射                |     |

| 表 5-6 DDR2 PHY 的时间参数              |     |

| 表 6-1 NAND Flash 控制器引脚描述          |     |

| 表 6-2 NAND Flash 控制器的命令           |     |

| 表 6-3 NAND Flash 控制器支持的特殊命令       |     |

| 表 7-1 USB2.0 OTG 控制器引脚描述          |     |

| 表 7-2 buffer 状态域定义                |     |

| 表 9-1 LCD 控制器引脚描述                 |     |

| 表 9-2 LCD 控制器的工作时序参数              |     |

| 表 10-1 SD/SDIO 主控制器信号描述           |     |

| 表 10-2 描述符 DESO                   |     |

| 表 10-3 描述符 DES1                   |     |

| 表 10-4 描述符 DES2                   |     |

| 表 10-5 描述符 DES3                   |     |

| 表 11-1 传输类型及参数更新方式                |     |

| 表 11-2 DMA 的外设硬件接口号               |     |

| 表 11-3 DMA 传输类型及流控编码              |     |

| 表 11-4 DMA 传输长度 MSIZE 编码          | 181 |

| 表 11-5 DMA 传输宽度              | 181 |

|------------------------------|-----|

| 表 12-1 GSC3280 中断控制器中断源列表    | 187 |

| 表 13-1 EMI 接口引脚描述            | 190 |

| 表 14-1 SPI 控制器引脚描述           | 195 |

| 表 15-1 UART 引脚描述             | 202 |

| 表 16-1 I2C 控制器引脚描述           | 208 |

| 表 16-2 I2C_CLK 最小频率与 SCL 的关系 | 211 |

| 表 17-1 I2S 控制器引脚描述           | 218 |

| 表 18-1 PS2 控制器引脚描述           | 228 |

| 表 18-2 PS2 控制器命令字            | 230 |

| 表 19-1 7816 接口控制器 0 的引脚描述    | 232 |

| 表 19-2 7816 接口控制器 1 的引脚描述    | 232 |

| 表 21-1 CAN 控制器引脚描述           | 243 |

| 表 21-2 错误状态表                 | 248 |

| 表 21-3 错误计数值的变动条件表           | 248 |

| 表 21-4 标准帧单过滤模式验收数据过滤对应表     | 250 |

| 表 21-5 扩展帧单过滤模式验收数据过滤对应表     | 251 |

| 表 21-6 标准帧双过滤模式验收数据过滤对应表     | 252 |

| 表 21-7 扩展帧双过滤模式验收数据过滤对应表     | 252 |

| 表 21-8 仲裁丢失位置对应表             | 253 |

| 表 22-1 ADC 与触摸屏控制器引脚描述       | 255 |

| 表 22-2 ADC 与触摸屏控制器命令         | 260 |

| 表 23-1 PWM 与旋转编码器接口的引脚描述     | 263 |

| 表 26-1 GPIO 与引脚的对应关系         | 283 |

| 表 27-1 GSC3280 产品描述          | 288 |

| 表 28-1 GSC3280 用户手册修订历史      | 289 |

# 1产品概览

# 1.1 产品简介

GSC3280 芯片是一款主要面向工业终端类应用的 SOC 芯片,采用 0.13um 标准 CMOS 制造工艺,主频 200~266MHZ。GSC3280 以 32 位龙芯处理器作为主控处理器,并在片内集成了丰富的功能模块与外围设备,包括 10/100Mbps 以太网 MAC 控制器、USB2.0 OTG 控制器、DDR2 控制器、NAND Flash 控制器、SD/SDIO 主控制器、LCD 控制器、I2C、I2S、UART、SPI、PWM、旋转编码器鉴相器、定时器等等;丰富的片内集成设备提高了整体性能,降低了系统成本,并可以满足更多的应用需求。

GSC3280 芯片的一个显著特征是采用了 32 位龙芯处理器作为主控处理器。32 位龙芯处理器是一款 7级流水乱序执行 RISC 处理器,具有独立的 16KB 指令 cache 与 16KB 数据 cache, 支持 MMU,可以运行 Linux、WinCE、VxWorks 等主流操作系统。

GSC3280 内部总线架构采用了主流的 AXI、AHB、APB 总线,并针对片内设备的特点与应用需求进行了一系列设计结构优化,提高了系统性能与数据吞吐率。同时,GSC3280 芯片采用了一系列的低功耗优化措施,包括休眠模式、关闭无用时钟、低频运行等,软硬件的配合可以显著降低整个芯片的功耗。针对具体应用,通过软硬件优化措施,GSC3280 芯片可在性能、功耗、灵活性等方面达到一个最佳的平衡。

GSC3280 芯片具有较好的通用性,除了云计算、工业控制、税控终端、智能电网集中器等终端类应用之外,还可以拓展应用于不同的相关领域,例如信息安全领域。

GSC3280 芯片集成了丰富的片上功能,本手册后续部分将分别对此进行详细的介绍。 GSC3280 芯片主要集成了如下的片上功能:

- 32 位龙芯处理器作为主控处理

- 支持 NAND Flash、NOR Flash 与 SPI 三种启动模式

- DDR2 控制器,最高支持 16x533Mbps 数据传输速率

- NAND Flash 控制器,支持 8 位 SLC/MLC NAND Flash 颗粒

- 外部静态存储器接口(EMI接口),支持 NOR Flash 与 SRAM

- 10/100Mbps 自适应以太网 MAC 控制器

- USB2.0 OTG 控制器

- SD/ SDIO 主控制器

- TFT LCD 控制器,最大支持分辨率为 1440x900

- 多通道 DMA 控制器

- 可编程中断控制器

- 1路旋转编码器接口与3通道PWM接口,支持电机控制PWM与普通PWM

- 8 个 UART 接口,支持包括 2/3/8 线以及 232/485 等不同类型的串口

- 2 个 SPI 主机接口

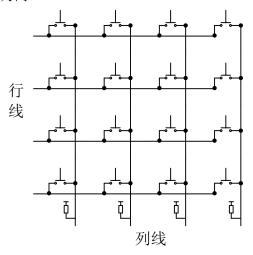

- 4x4 矩阵键盘接口

- 2 个 7816 主机接口

- 1 个 I2C 主机接口

- 1 个 I2S 主机接口

- 2 个 PS2 主机接口

- 1 个 CAN2.0B 接口

- 4路 ADC 与触摸屏接口

- 4个可编程定时器

- 1个看门狗定时器

- 88 个可编程 GPIO 引脚与 32 个外部中断源

- 片上可编程 PLL 时钟发生器

# 1.2 功能特性

#### 龙芯处理器

- 32 位 RISC 体系结构

- 7级乱序执行流水线

- 包含硬件乘法器与除法器

- 16KB 指令 cache 与 16KB 数据 cache

- 关键字优先与非阻塞 cache

- 支持 MMU 并包含 32 项 TLB

- 支持 EJTAG 片上调试功能

- 采用 AXI 接口

- 支持 Linux、WinCE 等主流操作系统

#### 三种启动模式

- NAND Flash 启动

- SPI Flash 启动

- NOR Flash 启动

- 通过引脚配置选择启动模式

#### DDR2 内存控制器

- 最高数据传输速率为 16x600Mbps

- 16 位数据位宽

- 最大支持 256MB 存储容量

- 支持1个 rank

- 软件可配置 PHY 时序

#### NAND Flash 控制器

- 支持 8 位 SLC/MLC NAND Flash 颗粒

- 支持 2KB/4KB 页大小

- 支持硬件 BCH ECC 校验码

- 支持省电模式

- 读写时序参数可配置

- 具有启动功能

- 内置 DMA 引擎

# 外部静态存储器接口(EMI接口)

- 支持 8 位异步 SRAM 与 NOR Flash

- 支持 NOR Flash 启动

- 最大支持3个片外设备

- 对于非 SRAM 类型的设备可支持 READY 握手信号

- 有限支持同步 SRAM 与 NOR Flash

#### 10/100Mbps 以太网 MAC 控制器

- 支持 IEEE 802.3 协议

- 支持标准 MII/RMII 接口

- 支持 10/100Mbps 传输速率

- 支持全双工和半双工操作模式

- 内置接收和发送 DMA

- 自动丢弃错误帧

- 支持对特殊 MAC 地址的检测

- Hash 表支持对单播和多播地址的匹配

- 支持混杂模式,即可接收 LAN 中所有帧

- 支持 VLAN 帧的识别

- 支持 IP 报文头部 checksum 字段检验

- 支持 TCP/IP 报文中 checksum 字段插入

#### USB2.0 OTG 控制器

- 支持主机与设备模式

- 支持非点对点模式(即支持 HUB)

- 内置 DMA 引擎

- 主机模式下共有 8 个 channel

- 设备模式下共有 5 个 endpoints

- 内部 FIFO 大小为 1024x35bit

#### SD/SDI0 主控制器

- 支持 SD2.0 协议

- 支持 SDIO2.0 协议

- 支持卡的热插拔

- 数据位宽支持1位与4位

- 内置 DMA 引擎

#### TFT LCD 控制器

- 支持 8、16 位色深的 TFT 屏

- 支持可编程视频时序

- 支持可编程视频分辨率,最大支持分辨率为 1440x900

- 支持可编程视频控制信号电平极性

- 支持大范围的输入时钟频率

- 支持硬件光标

#### 多通道 DMA 控制器

- 4 通道 DMA

- 支持存储器到存储器、存储器到外设、 外设到存储器、外设到外设等传输类型

- 支持 single-block 与 multi-block 传输

- 支持软件握手与硬件握手的 DMA 请求

- 支持 16 个硬件握手请求

#### 可编程中断控制器

- 支持 31 个中断源

- 高电平触发中断

- 每一个中断可分别进行使能与屏蔽

- 所有中断源具有相同的中断优先级

- 软件可强制某一个中断源产生中断

- 可在时钟关闭的情况下接收中断并向 CPU 发出中断请求

#### SPI 主机接口

- 2个 SPI 接口,均为主机模式

- SPI1 接口支持启动功能

- 支持查询、中断和 DMA 传输模式

- 支持 256 种波特率

- 支持 Byte Sleep

- 数据帧长度可配置为 2-17 位

- 支持 MSB 优先或 LSB 优先

- 支持全双工通信

- 支持全部四种 SPI 模式

#### 4x4 矩阵键盘接口

- 支持最大 4x4 矩阵键盘

- 待机模式下可通过按键产生唤醒中断

- 支持单键与同时按下任意两个键的情况

#### 7816 主机接口

- 两个 7816 主机接口

- 支持 ISO7816-3 协议

- 异步半双工模式

- 支持 T=0 协议

- 支持可编程波特率

- 支持正向模式和反向模式

- 支持奇偶校验。

- 支持自动重传

# 3 通道 PWM 与旋转编码器接口

- 支持 3 个独立的 PWM 通道

- 支持一个增量式旋转编码器

- PWM 支持两种工作模式: 普通 PWM 模式与电机控制 PWM 模式

- PWM模式下可以产生6个单边沿输出、3个双边沿输出或者混合输出

- PWM 模式下未用通道可用作定时器

- 电机 PWM 模式下每个通道产生两个极 性相反的输出

- 支持3个捕获输入

- 支持1个快速终止输入

## UART

- 8个 UART,均兼容 16550a

- 支持 5~8 位数据位

- 支持 1/1.5/2 位停止位

- UARTO/1/2/7 支持 2 线 232 连接

- UART3/4/5 支持 3 线 485 连接

- UART6 支持 8 线全功能串口

- UART3/4/5/6 支持 DMA 传输

- UART7 支持红外接口

- 232 连接支持最大波特率 3.7Mbps

- 485 连接支持最大波特率 12Mbps

#### I2C 主机接口

- 支持主机模式

- 支持标准、快速与高速三种传输速率

- 支持 7/10 位寻址方式

- 支持查询、中断与 DMA 传输方式

#### 12S 主机接口

- 支持主机模式

- 1个接收通道与1个发送通道

- 支持 12/16/20/24/32 位采样宽度

● 支持 DMA 传输模式

## PS2 主机接口

- 支持两个 PS2 主机接口

- 可用于连接鼠标和键盘

- 11 位数据帧格式

- 独立的发送与接收模块

- 支持查询和中断传输模式

#### CAN2. OB 接口

- 支持 CAN2.0B 协议,兼容 CAN2.0A 协议

- 支持标准帧与扩展帧

- 支持波特率 10K~1Mbps

- 可设置单过滤与双过滤两种过滤模式

- 具有休眠与唤醒功能

#### ADC 与触摸屏接口

- 4 通道 SAR 型 ADC

- 12 位精度

- 可用作 ADC 或者连接触摸屏

- 支持 4 线电阻触摸屏

- 支持最高采样率为 120Ksps

- 支持低功耗模式

#### 可编程定时器

- 4个32位定时器

- 每个定时器时钟独立可配置

- 支持循环定时与单次定时两种工作模 式

#### 看门狗定时器

- 32 位看门狗定时器

- 可配置看门狗定时器计数时钟

- 发生超时的时候,允许直接产生系统复 位信号,也允许先产生中断再产生系统 ● LFBGA256 封装 复位信号

# 可编程 GPIO 引脚

## 1.3 结构框图

- 88 个 GPIO 引脚,每个引脚独立可配置

- 其中 32 个 GPIO 可用作外部中断源

- 支持高电平、低电平、上升沿、下降沿 等4种中断触发模式

- 具有内部消抖电路可用于对外部中断 源输入进行消抖

# 片上 PLL

- 输出频率范围 62.5MHZ~1500MHZ

- 外部引脚可配置 8 种 PLL 输出频率

- 运行时软件可灵活配置 PLL 输出频率

#### 工作电压

- 核心电压: 1.2V

- IO 电压: 3.3V

- DDR2 接口电压: 1.8V

- USB2.0 OTG 数字电压: 1.2V

- USB2.0 OTG 模拟电压: 3.3V

- PLL 模拟电压: 1.2V

- PLL 数字电压: 1.2V

- ADC 模拟电压: 3.3V

- ADC 数字电压: 1.2V

#### 温度范围

-40℃~85℃

#### 工作频率

- DDR2 PHY 最高工作频率 600MHZ

- CPU 最高工作频率 300MHZ

- AXI 总线最高工作频率 300MHZ

- AHB 总线最高工作频率 200MHZ

- APB 总线最高工作频率 66.7MHZ

#### 封装

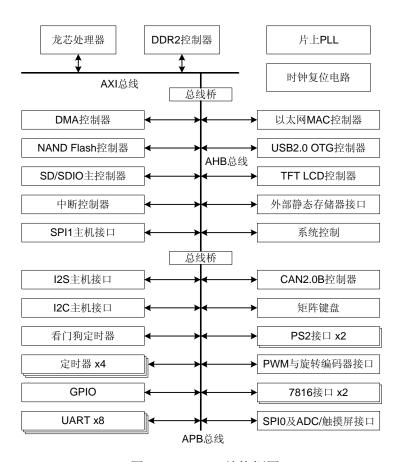

GSC3280 芯片以龙芯处理器为核心,集成了丰富的片上设备,所有的功能模块通过 AMBA 总线进行连接,包括 AXI 总线、AHB 总线以及 APB 总线,构成了一个独立的片上系统。GSC3280 芯片的整体结构框图如图 1-1 所示。

图 1-1 GSC3280 结构框图

# 2 存储空间

# 2.1 地址映射

GSC3280 芯片以 32 位龙芯处理器作为中央处理器,具有 4GB 的存储器逻辑地址空间, 所有设备与存储器采用统一编址的方式;对于设备内部的控制与状态寄存器,由于映射到存储器空间,因此可以采用与访问存储器一样的访问方式。

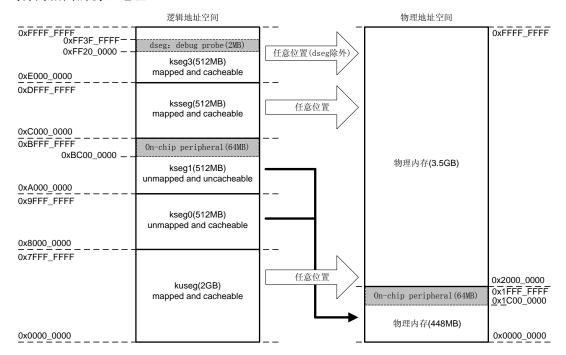

在 32 位龙芯处理器的体系结构中,将逻辑地址空间划分为 5 个地址段,分别为 kuseg、kseg0、kseg1、ksseg 以及 kseg3,如图 2-1 所示; 其中 kuseg、ksseg、kseg3 可以映射到物理地址中的任意位置,而 kseg0、kseg1 则固定映射到物理地址的最低 512MB 空间。对于低512MB 物理地址空间,由于可以从不同的逻辑地址空间映射过来,因此可以通过不同的方式访问相同的物理地址。

图 2-1 龙芯处理器逻辑地址空间与物理地址空间的映射关系

GSC3280 芯片中所有设备与存储器采用统一编址的方式,所有片内设备的逻辑地址映射到 kseg1 中从 0xBC00\_0000 开始的 64MB 空间,对应于物理地址中从 0x1C00\_0000 开始的 64MB 空间。通过访问相应的存储器逻辑地址,在芯片内部自动转换为对应的物理地址,就可以访问到设备中对应的控制与状态寄存器,从而控制片内设备实现各种期望的功能。

在分配给片内设备单元的 64MB 地址空间中,针对不同的功能单元分别划分了 4KB、8KB 以及 256KB 不等大小的空间,如表 2-1 所示。表 2-1 给出了片内设备在 kseg1 段的逻辑地址空间,软件可以通过读写相应的 kseg1 段逻辑地址来访问与控制这些片内功能设备;如果必要,软件也可以通过其他地址段的逻辑地址来访问这些片内设备。

表 2-1 GSC3280 芯片的存储器地址映射表

| diameter tot. t.t |              |          |                |  |

|-------------------|--------------|----------|----------------|--|

| 物理基地址             | 逻辑基地址(kseg1) | 大小/Byte  | 功能单元           |  |

| 0x00000000        | 0xA0000000   | 448M     | 物理内存           |  |

| 0x1C000000        | 0xBC000000   | 256K     | USB2.0 OTG 控制器 |  |

| 0x1C040000        | 0xBC040000   | 8K       | LCD 控制器        |  |

| 0x1C042000        | 0xBC042000   | 8K       | DMA 控制器        |  |

| 0x1C044000        | 0xBC044000   | 8K       | NAND Flash 控制器 |  |

| 0x1C046000        | 0xBC046000   | 8K       | SD/SDIO 控制器    |  |

| 0x1C048000        | 0xBC048000   | 8K       | 中断控制器          |  |

| 0x1C04A000        | 0xBC04A000   | 8K       | 系统控制           |  |

| 0x1C04C000        | 0xBC04C000   | 8K       | SPI1 主机接口      |  |

| 0x1C04E000        | 0xBC04E000   | 8K       | 外部静态存储器接口控制器   |  |

| 0x1C055000        | 0xBC055000   | <u>-</u> | 保留             |  |

| 0x1C100000        | 0xBC100000   | 4K       | CAN 2.0B 控制器   |  |

| 0x1C101000        | 0xBC101000   | 4K       | SPIO 主机接口      |  |

| 0x1C102000        | 0xBC102000   | 4K       | 矩阵键盘           |  |

| 0x1C103000        | 0xBC103000   | 4K       | 7816-0 主机接口    |  |

| 0x1C104000        | 0xBC104000   | 4K       | 7816-1 主机接口    |  |

| 0x1C105000        | 0xBC105000   | 4K       | 旋转编码器与 PWM     |  |

| 0x1C106000        | 0xBC106000   | 4K       | PS/2-0 接口      |  |

| 0x1C107000        | 0xBC107000   | 4K       | PS/2-1 接口      |  |

| 0x1C108000        | 0xBC108000   | 4K       | UART0          |  |

| 0x1C109000        | 0xBC109000   | 4K       | UART1          |  |

| 0x1C10A000        | 0xBC10A000   | 4K       | UART2          |  |

| 0x1C10B000        | 0xBC10B000   | 4K       | UART3          |  |

| 0x1C10C000        | 0xBC10C000   | 4K       | UART4          |  |

| 0x1C10D000        | 0xBC10D000   | 4K       | UART5          |  |

| 0x1C10E000        | 0xBC10E000   | 4K       | UART6          |  |

| 0x1C10F000        | 0xBC10F000   | 4K       | UART7          |  |

| 0x1C110000        | 0xBC110000   | 4K       | 可编程输入输出接口      |  |

| 0x1C111000        | 0xBC111000   | 4K       | I2C 主机接口       |  |

| 0x1C112000        | 0xBC112000   | 4K       | I2S 主机接口       |  |

| 0x1C113000        | 0xBC113000   | 4K       | DDR2 控制器       |  |

| 0x1C114000        | 0xBC114000   | 4K       | 可编程定时器         |  |

| 0x1C115000        | 0xBC115000   | 4K       | 看门狗定时器         |  |

| 0x1C116000        | 0xBC116000   | 4K       | DDR2 PHY       |  |

| 0x1C117000        | 0xBC117000   | 8K       | 以太网 MAC 控制器    |  |

| 0x1C119000        | 0xBC119000   | -        | 保留             |  |

| 0x1DC00000        | 0xBDC00000   | 4M       | 外部静态存储器空间      |  |

| 0x1E000000        | 0xBE000000   | -        | 保留             |  |

| 0x1FC00000        | 0xBFC00000   | 4M       | 4MB 启动空间       |  |

| 0x20000000        | -            | 3.5G     | 物理内存           |  |

# 2.2 片内存储器

GSC3280 芯片所有片内设备映射到从 0x1C000000 开始的 64MB 物理地址空间,对应于kseg1 段从 0xBC000000 开始的 64MB 逻辑地址空间。在这 64MB 空间中,除了未实际使用的空间,其他绝大多数地址都用于各种控制与状态寄存器,只有 4KB 空间用于片内存储器。这 4KB 片内存储器是 NAND Flash 控制器的片内缓冲区,用于读写 NAND Flash 颗粒时对一个4KB 大小的页进行缓冲。该片内存储器分别映射到两个地址空间,分别为 0xBC044000 开始的 4KB 空间,用于 NAND Flash 控制器的数据缓冲,以及 0xBFC00000 开始的 4KB 地址空间,用于 NAND Flash 启动。当 NAND Flash 控制器不工作时,可以将这 4KB 片内存储器用作普通的数据存储区域,通过 0xBC044000 开始的 4KB 逻辑地址空间即可以访问该片内存储器。

# 2.3 片外存储器

GSC3280 芯片支持多种常用的片外存储器,为不同的应用提供了多样的选择,这些存储器类型包括有:

- DDR2 存储器:

- NAND Flash 存储器;

- NOR Flash 存储器;

- SPI 接口 NOR Flash 存储器:

- 静态存储器 (SRAM);

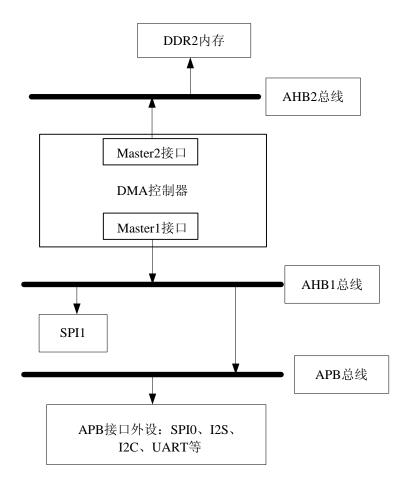

#### 2.3.1 DDR2 存储器

GSC3280 芯片集成了 DDR2 控制器,可支持最大 256MB 的 16 位 DDR2 存储器,最高数据传输速率可达 16x533Mbps。 DDR2 控制器有 AXI 和 AHB 两个主机端口,可区分不同接口类型和不同优先级的片内主设备,例如 CPU 和 DMA 请求。 DDR2 控制器提供了先进的配置特性,例如可配置端口带宽和读操作预取长度等,根据需要可由软件进行微调以优化带宽和延迟。

#### 2.3.2 NAND Flash 存储器

GSC3280 芯片集成了 ONFI 1.0 协议 NAND Flash 控制器,支持 8 位 NAND Flash 颗粒芯片,页大小可配置为 2KB 或者 4KB,采用的硬件校验算法为 BCH8,支持 NAND Flash 启动。

#### 2.3.3 NOR Flash 存储器

GSC3280 芯片 EMI 接口可配置用于连接片外 NOR Flash 芯片,支持的数据位宽为 8 位,最多可连接 3 片,每一片 NOR Flash 颗粒最大支持容量为 1MB,因此 GSC3280 最大支持 3MB 的 NOR Flash 存储器芯片。

# 2.3.4 SPI Flash 存储器

GSC3280 芯片集成了两个 SPI 主机接口,两个 SPI 接口都可以外接任意大小的 SPI Flash。 SPI1 接口支持系统从 SPI Flash 里启动,系统启动空间大小为 4MB,SPI0 接口不支持系统启动。在启动完成后,软件可通过正常的访问方式继续读写 SPI1 接口的 SPI Flash 芯片。

# 2.3.5 静态存储器

除了NOR Flash存储器,GSC3280芯片EMI接口也可配置用于连接片外静态存储器(SRAM)芯片。与外接 NOR Flash 存储器类似,支持的 SRAM 数据位宽为 8 位,最多可连接 3 片,每一片 SRAM 芯片最大支持容量为 1MB,因此 GSC3280 最大支持 3MB 的 SRAM 存储器芯片。

# 3 龙芯处理器

# 3.1 概述

GSC3280 芯片以 32 位龙芯处理器作为中央处理器,32 位龙芯处理器是一款由我国自主研发的 RISC 处理器,具有独立的 16KB 指令 cache 与 16KB 数据 cache,支持包含 32 项 TLB 的 MMU,并采用了一系列先进的体系结构设计技术,包括七级流水、动态调度、乱序执行、非阻塞 cache 等,具有出色的性能,可以运行 ucLinux、VxWorks、Linux、WinCE 等主流操作系统。

# 3.2 功能特性

32 位龙芯处理器具有如下的关键功能特性:

- RISC 体系结构

- 32 位地址与数据格式,采用小尾端次序

- 乱序执行内核,7级基本流水线

- 独立的 16KB 指令 cache 与 16KB 数据 cache, 分别为四路组相联结构

- 关键字优先与非阻塞 cache

- 支持 MMU,包含 32 项 TLB

- 硬件乘法器与除法器

- AMBA AXI 接口

- 支持 EJTAG 片上调试功能

#### 3.3 结构框图

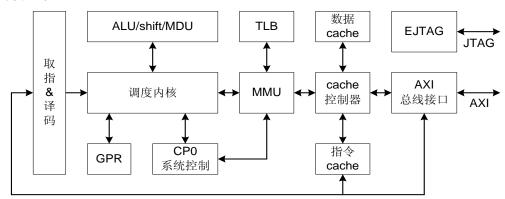

32 位龙芯处理器的结构框图如图 3-1 所示,主要组成部件包括有取指译码部件、调度内核、运算部件、MMU、CP0 协处理器、指令 cache、数据 cache、AXI 总线接口以及 EJTAG 调试单元等。

图 3-1 32 位龙芯结构框图

#### 3.4 流水线

32 位龙芯处理器内部具有七级基本流水线,采用了单发射乱序执行内核,通过寄存器重命名、动态调度以及转移预测等先进的体系结构技术,使得指令在处理器中可以不按照原始顺序执行,减缓或者消除了数据相关与控制相关带来了的流水线停顿,提高了流水线的执行效率与处理器的整体性能。

32 位龙芯处理器的七级基本流水线包括取指、译码、重命名、发射、执行、写回与提交共七个流水阶段;在取指阶段,CPU 访问 TLB 与指令 cache,取回需要的指令,并根据不同指令进行部分预先译码操作;在译码阶段,对取回的指令进行译码并转换为统一的内部编码;在重命名阶段,根据流水线中正在执行的各条指令的运行情况,对当前指令的逻辑寄存器进行动态重命名以解决相关问题;在发射阶段,当前指令读取通用寄存器堆的数据并发射到各执行部件中;在执行阶段,各执行部件从操作数都准备好的指令中选取最老的指令进行执行;在写回阶段,各运算部件将运算结果写回到指令重排队列中;在提交阶段,将指令重排队列中的指令运算结果写回到通用寄存器堆中,并更新相应的处理器状态。在没有流水线停顿的理想情况下,每一个流水节拍可以完成一条指令;而当出现数据相关、cache 不命中等情况时,则将引起流水线停顿,使得 CPU 无法一个节拍完成一条指令。

由于 32 位龙芯处理器的流水线是动态流水线,因此执行不同指令时所需要的流水级是不同的;对于大多数指令而言,通过七级基本流水线就可以完成执行;但某些复杂指令则需要更多的流水级节拍,例如访存指令流水线为八级,定点乘法与定点除法指令的流水线级数则根据操作数的不同而存在变化。

# 3.5 寄存器

32 位龙芯处理器提供了三类软件可见的寄存器: 32 个 32 位的通用寄存器、两个 32 位的整数乘法与除法运算结果寄存器、若干 32 位系统控制寄存器。

对于 32 个通用寄存器而言, r0 与 r31 是两个特殊的寄存器。其中 r0 寄存器硬连线为 0, 可以用作任何需要零值的指令的源寄存器; r0 也可以用作任何指令的目标寄存器,但 r0 寄存器的零值不会被更改,即该指令的运算结果将被丢弃。r31 寄存器除了用作普通的通用寄存器以外,还用于转移并链接指令的链接寄存器,即用于存储将来要返回的指令 PC。

定点乘法与除法结果寄存器 HI 与 LO 专门用于存储定点乘法的乘积与定点除法的商及余数,其中 HI 寄存器用于存储乘法结果的高 32 位或者除法结果的商,LO 寄存器用于存储乘法结果的低 32 位或者除法结果的余数。为了访问 HI 与 LO 寄存器,32 位龙芯处理器提供了MTHI、MTLO、MFHI、MFLO 等四条专门的指令。

系统控制寄存器主要用于存储管理、例外处理等系统控制功能,只能在内核状态下访问该类寄存器,有关系统控制寄存器的更多内容请看"CPO协处理器"一节。

# 3.6 存储管理

# 3.6.1 工作模式

32 位龙芯处理器支持四种工作模式:

● 用户模式(user mode)

- 监管模式(supervisor mode)

- 内核模式(kernel mode)

- 调试模式(debug mode)

32 位龙芯处理器支持最大 4GB 的逻辑地址空间,4GB 逻辑地址空间划分为不同的地址段,当处理器处于不同的工作模式时,对不同地址段具有不同的访问权限,虚实地址转换过程也会存在不同。

# 3.6.1.1 逻辑地址空间

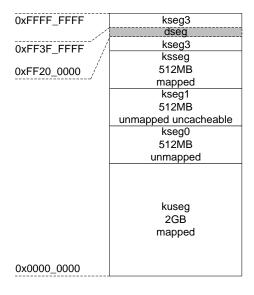

32 位龙芯处理器最大支持 4GB 逻辑地址空间,当处理器处于不同工作模式时,可以访问 4GB 逻辑地址空间的不同地址段,如图 3-2 所示。

在复位之后,或者发生例外的时候,龙芯处理器将进入到内核模式;在内核模式下,软件可以访问整个4GB逻辑地址空间以及CPO寄存器。

某些分层操作系统可由内核模式进入到监管模式,在监管模式下,软件只能访问 4GB 逻辑地址空间中的 suseg 段与 sseg 段;如果软件试图访问 suseg 段与 sseg 段之外的地址空间,则将触发一个地址错误例外;监管模式下不能访问 CPO 寄存器。

在用户模式下,软件只能访问 4GB 逻辑地址空间中的 useg 段;如果软件试图访问 useg 段之外的地址空间,则将触发一个地址错例外;用户模式下软件不能访问 CPO 寄存器。

| 虚拟地址                         | 用户模式             | 监管模式          | 内核模式  | 调试模式  |

|------------------------------|------------------|---------------|-------|-------|

| 0xFFFF_FFFF                  |                  |               |       | kseg3 |

| 0xF400_0000                  |                  | address error | kseg3 | dseg  |

| 0xF3FF_FFFF                  |                  |               |       | kseg3 |

| 0xF200_0000<br>0xF1FF_FFFF   |                  | sseg          | ksseg | ksseg |

| 0xE000_0000 /<br>0xDFFF_FFFF | address<br>error |               |       |       |

| 0xC000_0000<br>0xBFFF_FFFF   |                  | address       | kseg1 | kseg1 |

| 0xA000_0000                  |                  | error         |       |       |

| 0x9FFF_FFFF                  |                  |               | kseg0 | kseg0 |

| 0x8000_0000                  |                  |               |       |       |

| 0x7FFF_FFFF                  | useg             | suseg         | kuseg | kuseg |

| 0x0000_0000                  |                  |               |       |       |

图 3-2 32 位龙芯处理器的逻辑地址空间与地址段划分 当发生调试例外时,龙芯处理器将进入到调试模式,在调试模式下,软件除了具有和内

核模式一样的访问权限,额外还可以访问调试地址段 dseg;调试地址段 dseg 与内核模式下的 kseg3 地址段部分重叠,但 dseg 段的访问可以由软件打开或者关闭,因此在必要时调试模式下软件也可以访问完整的 kseg3 地址段。

图 3-2 中的每一个地址段或者是具有 mapped 属性或者具有 unmapped 属性,具体请看后续各工作模式的详细描述; 在虚实地址转换时, unmapped 地址段的虚拟地址不会使用 TLB,而是采用一种直接映射方式; 而 mapped 地址段的虚拟地址则通过 TLB 进行虚实地址映射,转换的单位是页,转换的信息包括物理页号、是否 cacheable 以及保护属性等。

# 3.6.1.2 用户模式

在用户模式下,软件只能访问 2GB 大小的逻辑地址空间,该地址空间称为 useg (用户段, user segment),起始于地址 0,结束于地址 0x7FFF\_FFFF,如图 3-3 所示。任何对 useg 空间以外逻辑地址的访问都将引起一个地址错误例外。

| 0xFFFF_FFFF |                       |

|-------------|-----------------------|

|             | address<br>error      |

| 0x8000_0000 |                       |

| 0x7FFF_FFFF |                       |

|             | useg<br>2GB<br>mapped |

| 0x0000_0000 |                       |

图 3-3 用户模式下的地址空间

当 CPO 寄存器中的 Status 寄存器同时包含如下状态位时,龙芯处理器将处于用户模式:

- KSU=10<sub>2</sub>

- EXL=0

- ERL=0

在用户模式下,除了上述 Status 寄存器的三个状态位,Debug 寄存器中的 DM 位也必须为 0.

useg 地址段的属性如表 3-1 所示,表明用户模式下软件可访问的虚拟地址的最高位必须为 0,即只能访问整个 4GB 逻辑地址空间中的低 2GB 空间,任何对高 2GB 地址空间的访问都将引起一个地址错误例外。对 useg 空间的访问将通过 TLB 进行虚实地址转换,在转换之前,虚拟地址将与 8 位的 ASID 域合并形成一个唯一的地址,该地址在经过 TLB 进行虚实地址转换之后产生对应的物理地址。在进行虚实地址转换时,TLB 表项中除了对应的物理页号信息,还包含了当前页是否使用 cache 的信息,即当前访问是直接访问外部存储器空间还是访问 cache。

|  | 地址位     | Status 寄存 |     | 字器  | Debug 寄存器 | 地址段名称 | 地址范围                       | 地址段大小 |

|--|---------|-----------|-----|-----|-----------|-------|----------------------------|-------|

|  |         | EXL       | ERL | KSU | DM        | 地址权石协 | 16개 16 B                   | 地址权人小 |

|  | A(31)=0 | 0         | 0   | 102 | 0         | useg  | 0x000_0000<br>~0x7FFF_FFFF | 2GB   |

表 3-1 用户模式下地址段属性

# 3.6.1.3 监管模式

在分层操作系统中,操作系统内核运行于内核模式下,而操作系统其余部分则运行于监管模式下。当 CPO 寄存器中的 Status 寄存器同时包含如下状态位时,龙芯处理器将处于监管模式:

- KSU=01<sub>2</sub>

- EXL=0

- ERL=0

在监管模式下,除了上述 Status 寄存器的三个状态位,Debug 寄存器中的 DM 位也必须为 0.

| 0xFFFF_FFFF | address                |

|-------------|------------------------|

| 0xE000_0000 | error                  |

| 0xDFFF_FFFF | sseg                   |

| 0xC000 0000 | 512MB<br>mapped        |

| 0xBFFF FFFF | ''                     |

| OXBITT_ITT  | address                |

| 0xA000_0000 | error                  |

| 0x9FFF_FFFF | address                |

| 0x8000_0000 | error                  |

| 0x7FFF_FFFF |                        |

|             | suseg<br>2GB<br>mapped |

| 0x0000_0000 |                        |

图 3-4 监管模式下的地址空间

监管模式下软件可访问的逻辑地址空间如图 3-4 所示,包括 suseg 与 sseg 两个地址段,地址段属性如表 3-2 所示。监管模式下的 suseg 地址段对应于用户模式下的 useg 地址段,地址范围为 0x0-0x7FFF\_FFFF,即整个 4GB 逻辑地址空间中的低 2GB 空间。监管模式下的 sseg 地址段大小为 512MB,即 32 位虚拟地址中最高三位地址为 1102。对 suseg 与 sseg 空间的访问都将通过 TLB 进行虚实地址转换,在转换之前,虚拟地址将与 8 位的 ASID 域合并形成一个唯一的地址,该地址在经过 TLB 进行虚实地址转换之后产生对应的物理地址。在进行虚实地址转换时,TLB 表项中除了对应的物理页号信息,还包含了当前页是否使用 cache 的信息,即当前访问是直接访问外部存储器空间还是访问 cache。

| 农 0 2 血 自 庆 2 1 2 2 1 2 1 2 1 |            |     |                 |           |        |              |         |  |  |

|-------------------------------|------------|-----|-----------------|-----------|--------|--------------|---------|--|--|

| 地址位                           | Status 寄存器 |     |                 | Debug 寄存器 | 地址段名称  | 地址范围         | 地址段大小   |  |  |

|                               | EXL        | ERL | KSU             | DM        | 地址权石阶  | 16개 161명<br> | 地址权人小   |  |  |

| A(31)=0                       |            |     |                 |           | cricoa | 0x000_0000   | 2GB     |  |  |

| A(31)-0                       | 0          | _   | 01              | 0         | suseg  | ~0x7FFF_FFFF | 206     |  |  |

| A(31:29)                      | U          | 0   | 01 <sub>2</sub> | U         | SSOG   | 0xC000_0000  | 512MB   |  |  |

| = 110 <sub>2</sub>            |            |     |                 |           | sseg   | ~0xDFFF_FFFF | STZIVID |  |  |

表 3-2 监管模式下地址段属性

# 3.6.1.4 内核模式

当 CPO 寄存器中的 Status 寄存器包含如下任意一个或者多个状态位时,龙芯处理器将处于内核模式:

- KSU=00<sub>2</sub>

- EXL=1

- ERL=1

在内核模式下,除了上述三个状态位,Debug 寄存器中的DM 位也必须为O.

| 0xFFFF_FFFF | kseg3                |

|-------------|----------------------|

|             | 512MB                |

| 0xE000_0000 | mapped               |

| 0xDFFF_FFFF | ksseg                |

| _           | 512MB                |

| 0xC000_0000 | mapped               |

| 0xBFFF_FFFF | kseg1                |

|             | 512MB                |

| 0xA000_0000 | unmapped uncacheable |

| 0x9FFF_FFFF | kseg0                |

|             | 512MB                |

| 0x8000_0000 | unmapped             |

| 0x7FFF_FFFF |                      |

|             |                      |

|             |                      |

|             | kuseg                |

|             | 2GB                  |

|             | mapped               |

|             |                      |

|             |                      |

| 0x0000_0000 |                      |

图 3-5 内核模式下的地址空间

当龙芯处理器发生一个例外并且该例外不是调试例外的时候,Status 寄存器的 EXL 位或者 ERL 位将会被置 1,处理器进入到内核状态开始进行例外处理;当完成例外处理的时候,可执行一条例外返回指令 ERET,处理器将跳转到此前发生例外的指令重新开始执行正常程序流程,同时将 EXL 位或者 ERL 位清零,此时处理器返回到发生例外之前的工作模式。

龙芯处理器在内核模式下可以访问整个 4GB 逻辑地址空间,如图 3-5 所示; 4GB 逻辑地址空间划分为不同的地址段,包括 kuseg、kseg0、kseg1、ksseg 以及 kseg3,不同地址段的属性如表 3-3 所示。

|                    | 1                                                 |         |     | THE COLUMN | 八十地址权两日 | _            | 1      |

|--------------------|---------------------------------------------------|---------|-----|------------|---------|--------------|--------|

| 地址位                | Status 寄存器                                        |         |     | Debug 寄存器  | 地址段名称   | 地址范围         | 地址段大小  |

|                    | EXL                                               | EXL ERL | KSU | DM         | 地址权石协   | 10 전 10 11   | 地址权人小  |

| A/21\-0            | EXL=1<br>或者<br>ERL=1<br>或者<br>KSU=00 <sub>2</sub> |         |     | 0          | kuseg   | 0x000_0000   | 2GB    |

| A(31)=0            |                                                   |         |     |            |         | ~0x7FFF_FFFF |        |

| A(31:29)           |                                                   |         |     |            | kseg0   | 0x8000_0000  | 512MB  |

| = 100 <sub>2</sub> |                                                   |         |     |            |         | ~0x9FFF_FFFF |        |

| A(31:29)           |                                                   |         |     |            | kseg1   | 0xA000_0000  | 512MB  |

| = 101 <sub>2</sub> |                                                   |         |     |            |         | ~0xBFFF_FFFF |        |

| A(31:29)           |                                                   |         |     |            | ksseg   | 0xC000_0000  | 512MB  |

| = 110 <sub>2</sub> |                                                   |         |     |            |         | ~0xDFFF_FFFF |        |

| A(31:29)           |                                                   |         |     |            | lscog2  | 0xE000_0000  | 512MB  |

| = 111 <sub>2</sub> |                                                   |         |     |            | kseg3   | ~0xFFFF_FFFF | STZIND |

表 3-3 内核模式下地址段属性

内核模式下 kuseg 地址段对应于用户模式下的 useg 地址段与监管模式下的 suseg 地址段,地址范围为 0x0-0x7FFF\_FFFF,即整个 4GB 逻辑地址空间中的低 2GB 空间。正常情况下,内核模式下对 kuseg 段的访问将通过 TLB 进行虚实地址转换,在转换之前,虚拟地址将与 8 位的 ASID 域合并形成一个唯一的地址,该地址在经过 TLB 进行虚实地址转换之后产生对应的物理地址。在进行虚实地址转换时,TLB 表项中除了对应的物理页号信息,还包含了当前页是否使用 cache 的信息,即当前访问是直接访问外部存储器空间还是访问 cache。

内核模式下 kseg0 地址段的范围为 0x8000\_0000-0x9FFF\_FFFF,大小为 512MB,对应于 32 位虚拟地址中最高三位地址为 100<sub>2</sub>; kseg0 地址段具有 unmapped 属性,因此对 kseg0 段的访问不会经过 TLB 进行虚实地址转换,而是从虚拟地址直接减去 0x8000\_0000 作为物理地址。Config 寄存器中的 KO 域控制 kseg0 段是否使用 cache,即当前访问是直接访问外部存储器空间还是访问 cache。

内核模式下 kseg1 地址段的范围为  $0xA000\_0000-0xBFFF\_FFFF$ ,大小为 512MB,对应于 32 位虚拟地址中最高三位为  $101_2$ ; kseg1 地址段具有 unmapped 和 uncacheable 属性,因此 对 kseg1 段的访问不会经过 TLB 进行虚实地址转换,而是从虚拟地址直接减去  $0xA000\_0000$  作为物理地址,该物理地址将用于直接访问外部存储器空间。

内核模式下 ksseg 地址段的范围为 0xC000\_0000-0xDFFF\_FFFF,大小为 512MB,对应于 32 位虚拟地址中最高三位为 110<sub>2</sub>; kseg3 地址段的范围为 0xE000\_0000-0xFFFF\_FFFF,大小为 512MB,对应于 32 位虚拟地址空间中最高三位为 111<sub>2</sub>; 对 ksseg 段与 kseg3 段的访问将通过 TLB 进行虚实地址转换,在转换之前,虚拟地址将与 8 位的 ASID 域合并形成一个唯一的地址,该地址在经过 TLB 进行虚实地址转换之后产生对应的物理地址。在进行虚实地址转换时,TLB 表项中除了对应的物理页号信息,还包含了当前页是否使用 cache 的信息,即当前访问是直接访问外部存储器空间还是访问 cache。

# 3.6.1.5 调试模式

图 3-6 调试模式下的地址空间

当发生调试例外时,Debug 寄存器中的 DM 位为 1,龙芯处理器进入到调试模式。除了额外可以访问调试地址段 dseg 之外,调试模式与内核模式具有相同的逻辑地址空间及访问权限;调试地址段 dseg 的地址范围为 0xFF20\_0000-0xFF3F\_FFFF,大小为 2MB,与 kseg3 地址段部分重叠,如图 3-6 所示。

dseg 地址段进一步划分为 dmseg 与 drseg 两个子地址段, 如表 3-4 所示; dmseg 地址段 的范围是 0xFF20 0000-0xFF2F FFFF,用于调试程序的程序数据存储空间; drseg 地址段的范 围是 0xFF30\_0000-0xFF3F\_FFFF,调试寄存器将映射到 drseg 地址段,通过访问 drseg 地址段 空间就可以访问调试寄存器。

表 3-4 dseg 地址段的划分与属性

| 地址段  | 子地址段              | 逻辑地址空间       | 物理地址空间                 | cache 属性     |

|------|-------------------|--------------|------------------------|--------------|

| dseg | dmseg             | 0xFF20_0000~ |                        |              |

|      |                   | 0xFF2F_FFFF  | dmseg 映射到调试主机 EJTAG 调试 | aa ab aa bla |

|      | 空间,drseg 映射为断点寄存器 | uncacheable  |                        |              |

|      | drseg             | 0xFF3F_FFFF  |                        |              |

dseg 地址段与 kseg3 地址段部分重叠,根据软件配置的不同,当访问这一段地址空间时, 硬件上既可以访问 dseg 段地址空间, 也可以访问 kseg3 段地址空间。处理器访问 drseg 地址 段的条件组合如表 3-5 所示,映射到 drseg 地址段的寄存器包括调试控制寄存器(DCR, Debug control register)与硬件断点寄存器,只允许软件以字的方式访问这些映射寄存器;如果访问 drseg 地址段中未映射到寄存器的空闲地址,则结果不可预知,软件应该避免这种情况;有 关 DCR 寄存器以及硬件断点寄存器的更多信息,请参考 EJTAG 规范。处理器访问 dmseg 地 址段的条件组合如表 3-6 所示,其中应当尽量避免 ProbEN 控制位为 0 时访问 dmseg 地址段 的情况,如果出现这种情况,则对 dmseg 地址段的任何访问都不能正常完成,处理器将处 于停顿状态,直到 ProbEN 控制位重新变为 1。

表 3-5 drseg 地址段的访问

| 操作         | Debug 寄存器的 LSNW 位 | 访问目标  |

|------------|-------------------|-------|

| Load/Store | 1                 | kseg3 |

| Fetch      | Don't care        | ducos |

| Load/Store | 0                 | drseg |

表 3-6 dmseg 地址段的访问

| 操作         | DCR 寄存器中的 ProbEN 位 | Debug 寄存器中的 LSNW 位 | 访问目标          |  |

|------------|--------------------|--------------------|---------------|--|

| Load/Store | Don't care         | 1                  | kseg3         |  |

| Fetch      | 1                  | Don't care         | dwaaa         |  |

| Load/Store | 1                  | 0                  | dmseg         |  |

| Fetch      | 0                  | Don't care         | 尽量避免          |  |

| Load/Store | 0                  | 0                  | <b>心里</b> 世 兄 |  |

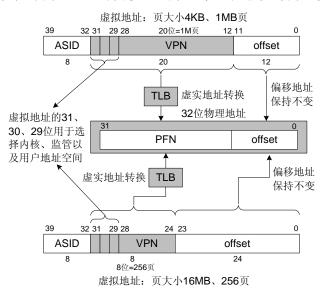

#### 3.6.2 TLB

32 位龙芯处理器支持全功能 MMU 并通过片内 TLB 进行虚实地址转换, 其中片内 TLB 包括 32 个表项, 采用全相联映射结构, 取指请求与数据访问均通过这 32 项 TLB 进行虚实地 址转换。每一个 TLB 表项对应于奇数页与偶数页两个子表项,因此 32 项 TLB 一共可以实现 64 个操作系统页的虚实地址转换。在一次虚实地址转换过程中,虚拟地址(即逻辑地址, 下同)与 EntryHI 寄存器中的 ASID 域进行合并扩展,合并扩展后的值用于并行查询 TLB 中的 所有表项,如果与某一个 TLB 表项匹配,则表明 TLB 命中,该 TLB 表项中的物理地址即为虚 拟地址对应的物理地址。

32 位龙芯处理器可以支持不同页大小的虚实地址转换,页的大小可以从 4KB 到 16MB,每一个数值都是前一个数值的 4 倍,因此页大小包括 4KB、16KB、64KB、256KB、1MB、4MB 与 16MB 等情况。

当一个虚拟地址在 TLB 中找到一个匹配项时,即 TLB 命中,此时从 TLB 中读出对应的物理页号,并与偏移地址合并形成最终的物理地址。当一个虚拟地址在 TLB 中不能找到匹配项时,即发生 TLB 缺失,此时产生一个 TLB 缺失例外,软件将从内存中把页表填写到 TLB 中。在软件写入 TLB 表项时,既可以随机写入到一个表项位置,也可以通过硬件机制写入到一个特定的 TLB 表项位置。

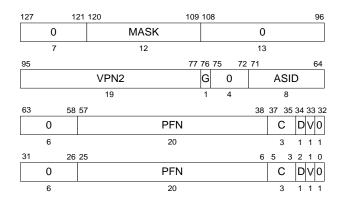

图 3-7 TLB 表项格式 表 3-7 TLB 表项位域说明

| 位域                                                         | 位宽 | 功能描述                                                                                                                              |                                         |  |  |

|------------------------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|

|                                                            |    | 域中的若干位,使之不参加判断 TLB                                                                                                                | 据页的大小,页屏蔽位用于屏蔽 VPN2<br>命中与否的地址比较,页屏蔽位与页 |  |  |

|                                                            |    | 大小的对应关系如下:<br>_ 页屏蔽位                                                                                                              | 页大小                                     |  |  |

|                                                            |    | 0000_0000_0000                                                                                                                    | 4KB                                     |  |  |

| MASK                                                       | 12 | 0000_0000_0011                                                                                                                    | 16KB                                    |  |  |

|                                                            |    | 0000_0000_1111                                                                                                                    | 64KB                                    |  |  |

|                                                            |    | 0000_0011_1111                                                                                                                    | 256KB                                   |  |  |

|                                                            |    | 0000_1111_1111                                                                                                                    | 1MB                                     |  |  |

|                                                            |    | _0011_1111_1111                                                                                                                   | 4MB                                     |  |  |

|                                                            |    | 1111_1111_1111                                                                                                                    | 16MB                                    |  |  |

| VPN2                                                       | 19 | 虚拟页号除以 2 之后的值;由于在 TLB 表项中一个虚拟页对应于一对奇偶物理页,因此虚拟页号需要除以 2; VPN2[18:10]总是会参加判断 TLB 命中与否的地址比较,而 VPN2[11:0]则根据 MASK 域中指定的页大小来决定是否参加地址比较。 |                                         |  |  |

| G                                                          | 1  | 全局位;当 G 域被设置为 1 时,表明当天 TLB 表项适用于所有的进程,因而在判断 TLB 是否命中时 ASID 域不再参与地址比较。                                                             |                                         |  |  |

| ASID 8 地址空间标志符;用于标志当前 TLB 表项所属的进程。                         |    |                                                                                                                                   |                                         |  |  |

| PFN 20 物理页号; 定义了物理地址的[31:12]位, 当页大小大于 4KB 时, 该际只有部分位会被使用到。 |    |                                                                                                                                   |                                         |  |  |

| С                                                          | 3  | cache 属性; C 域用于标志当前页的 cache 属性,在 32 位龙芯处理器中,C 域值为 $011_2$ 表示当前页具有 cacheable 属性,即访问当前页将使用 cache,                                   |                                         |  |  |

| 位域 | 位宽 | 功能描述                                                                                  |  |  |

|----|----|---------------------------------------------------------------------------------------|--|--|

|    |    | 所有其他值均表示具有 uncacheable 属性,即不使用 cache。                                                 |  |  |

| D  | 1  | Dirty 位; D 域表示当前页是否可写,为 1 时允许对当前页进行写操作,为 0 时不允许对当前页进行写操作,否则将引起一个 TLB modified 例外。     |  |  |

| V  | 1  | Valid 位; V 域表示当前 TLB 表项是否有效,当为 1 时,访问当前页可正常进行虚实地址转换,当为 0 时,访问当前页将引起一个 TLB invalid 例外。 |  |  |

TLB 表项的格式如图 3-7 所示,表项中每个域的说明如表 3-7 所示。软件通过 TLBWI 或者 TLBWR 指令向 TLB 中写入一个表项,在写入之前,需要先配置若干 CPO 寄存器以更新要写入的信息,这些 CPO 寄存器及其位域包括:

- PageMask 寄存器中的 MASK 域

- EntryHi 寄存器中的 VPN2 与 ASID 域

- EntryLo0 寄存器中的 PFN、C、D、V 和 G 域

- EntryLo1 寄存器中的 PFN、C、D、V 和 G 域

在上述 CPO 寄存器位域中,G 域同时存在于 EntryLoO 寄存器与 EntryLo1 寄存器中,写入到 TLB 表项中的 G 域值是两个寄存器中的 G 域值相"与"的结果。ASID 域用于减少上下文切换时引起的 TLB 抖动;在虚实地址转换时,EntryHi 寄存器中的 ASID 域与 TLB 表项中的 ASID 域将进行比较;通过 ASID 域,使得不同的进程信息可以共存于 TLB 与 cache 中。

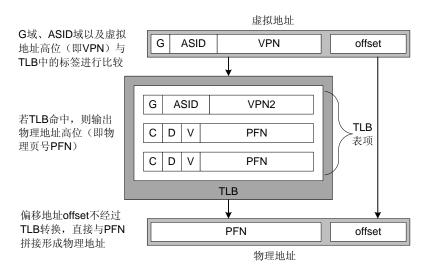

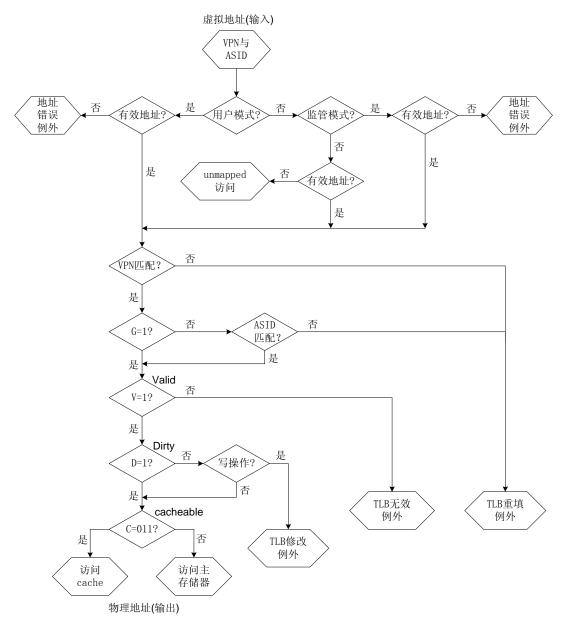

### 3.6.3 虚实地址转换

在虚实地址转换过程中,如果虚拟地址的虚拟页号与 TLB 表项的 VPN2 域互相匹配,并且满足如下两个条件之一,则称为一次 TLB 命中:

- TLB 表项中奇数页与偶数页的 G 域均为 1;

- EntryHi 寄存器中的 ASID 域与 TLB 表项的 ASID 域相等:

如果不满足以上匹配条件,则龙芯处理器发生一次 TLB 缺失例外,软件将从内存中读出对应的页表项写入 TLB。

图 3-8 虚实地址转换过程

虚实地址转换过程如图 3-8 所示,虚拟地址与 8 位 ASID 值进行合并扩展,扩展之后的值用于判断是否 TLB 命中; 8 位 ASID 是当前进程的标志信息,存储于 EntryHi 寄存器中.如果一个虚拟地址在 TLB 中命中,则读出对应 TLB 表项中的物理页号 PFN,并与虚拟地址中的偏

移地址拼接形成物理地址;偏移地址代表了当前请求在一页中的具体位置,偏移地址不需要进行虚实地址转换。

图 3-9 中表示了龙芯处理器在页大小为 4KB 与 16MB 时的虚实地址转换过程。偏移地址的长度由页大小决定,页大小为 4KB 时偏移地址为 12 位,虚拟地址中剩余的 20 位地址为虚拟页号 (VPN);页大小为 16MB 时偏移地址为 24 位,虚拟页号为 8 位。

图 3-9 龙芯处理器 32 位虚实地址转换过程图示

对于一个虚拟地址访问请求,如果在 TLB 中命中一个有效的 TLB 表项,则转换产生有效的物理地址;如果在 TLB 中不命中,则产生一个 TLB 缺失例外;如果 TLB 命中但对应的 TLB 表项无效,则产生一个 TLB 无效例外;图 3-10 给出了虚实地址转换及产生例外的流程。

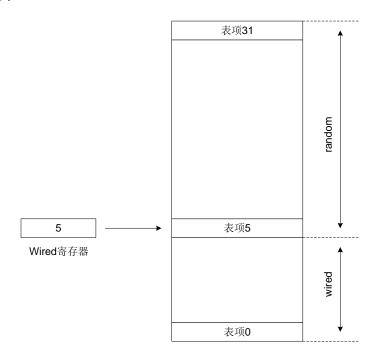

在软件向 TLB 中写入一个新的 TLB 表项时,既可以通过 Index 寄存器将 TLB 表项写入到一个确定的位置,也可以通过 Random 寄存器将 TLB 表项写入到一个随机的位置;对于随机写入的方式,还可以通过 Wired 寄存器使得某些 TLB 表项不会被替换。与此同时,根据实际情况的需要,软件还可以通过 PageMask 寄存器设置 TLB 表项中页的大小,页大小的范围为4KB 到 16MB。有关与存储管理相关 CPO 寄存器的详细描述,请看"CPO 协处理器"一章。

图 3-10 TLB 虚实地址转换流程

### 3.7 高速缓存

### 3.7.1 概述

32 位龙芯处理器具有独立的 16KB 片上 L1 指令 cache 与 16KB 片上 L1 数据 cache,分别组织为四路组相联结构,每一路 cache 大小为 4KB,由 128 个 cache 块(通常也称为 cache 行或者 cacheline)组成,每个 cache 块大小为 32 个字节。龙芯处理器采用了虚拟地址作为 cache 索引与物理地址作为 cache 标签,因而可以并行进行虚实地址转换与 cache 访问,提高了 cache 的效率。为了尽可能提高流水线的效率,龙芯处理器采用了非阻塞(non-blocking) cache 与关键字优先等高效 cache 设计技术。

在运行过程中,如果取指请求与数据请求访问的是 uncacheable 存储器区域,则该请求

将旁路 cache,并通过龙芯处理器的 AXI 接口向外发出请求,如果访问的是 cacheable 区域,则直接访问 cache 进行读写操作,并在 cache 不命中时通过 AXI 接口向主存储器发出一个长度为 8 个字的突发访问请求。

### 3.7.2 组织结构

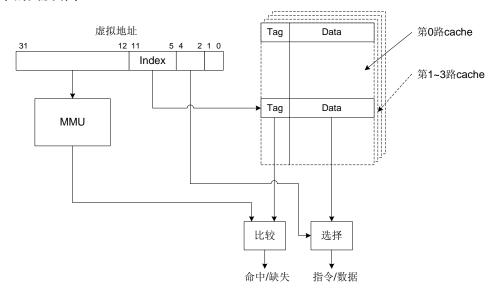

32 位龙芯处理器的指令 cache 与数据 cache 大小均为 16KB,分别采用四路组相联结构,如图 3-11 所示,其中每一路 cache 包括 128 个索引项,每个索引项对应于一个大小为 8 个字的 cache 块。在取指请求与数据请求的访问过程中,根据索引(Index)读取相应的标签(Tag)和数据(Data),读出的标签值用于和虚实地址转换产生的物理地址进行比较,从而确定哪一路 cache 包含了需要的数据。

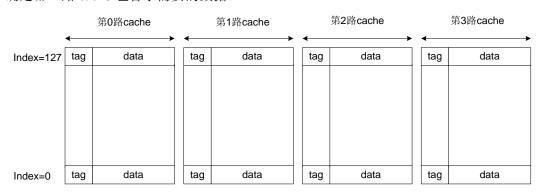

图 3-11 四路组相联 cache 组织结构

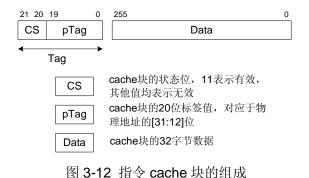

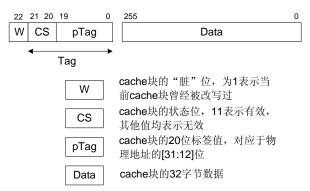

如图 3-11 所示,指令 cache 与数据 cache 具有相同的组织结构,每一路 cache 包括 128 个索引项,每一个索引项包含一个标签项与一个 8 个字的数据项,但指令 cache 与数据 cache 的标签项内容有所不同,如图 3-12 与图 3-13 所示,指令 cache 的标签项包含有 20 位的高位物理地址和 cache 块状态位,数据 cache 的标签项包含有 20 位的高位物理地址、cache 块状态位以及 cache 块是否为"脏"的 W 标志位。

北京神州龙芯集成电路设计有限公司 版权所有

图 3-13 数据 cache 块的组成

在一次 cache 访问过程中,虚拟地址的低 12 位用作 cache 的索引,其中[11:5]位用于索引每一路 cache 中的 128 个 cache 行,[4:2]位用于索引每一个 cache 块中的 8 个字,如图 3-14 所示;虚拟地址的高位用于通过 MMU 进行虚实地址转换,转换得到的物理地址与 cache 标签中的 pTag 进行比较,如果存在某一路的 pTag 与其匹配,并且 cache 标签的状态位有效,则称为一次"cache 命中(cache hit)",从数据项中得到需要的数据,如果四路 cache 中任何一路的 pTag 都不与其匹配,则称为一次"cache 缺失(cache miss)",将向内存发起一个8 个字的突发请求。

图 3-14 cache 访问过程

### 3.7.3 替换策略

龙芯处理器的 cache 采用了随机替换策略, 当一个请求在 cache 中不命中(cache 缺失)时,将从四路 cache 中随机选择一路进行替换,并把从内存读入的新 cache 块写入到被替换的位置。

龙芯处理器的 cache 是 write-back cache,因此不管是取指请求、读数据请求还是写数据请求引起 cache 缺失,都将首先从内存中读入对应的 cache 块到 cache 中,然后再进行取指或者数据读写操作。

在数据 cache 发生替换时,如果被替换的 cache 块状态有效(即 CS=0x3)并且 W 位为 1,则表明该 cache 块的数据曾经被改写过,当前 cache 块的数据是最新的数据,因此需要将当前被替换的 cache 块数据写回到内存中,否则直接丢弃即可。

### 3.7.4 cache 操作

32 位龙芯处理器提供了六条 cache 指令对 cache 进行各种细粒度的操作,包括使某个 cache 块无效、读出 cache 标签、写入 cache 标签以及使命中的 cache 行无效等。指令 cache 与数据 cache 均为四路组相联结构,使用访问地址的最低两位来区分当前 cache 指令是对哪一路 cache 进行操作。在六条 cache 中,一条用于指令 cache,五条用于数据 cache,具体情况如下表 3-8 所示。

| cache 指令的[20:16]位 | cache 操作                   | 目标 cache |

|-------------------|----------------------------|----------|

| 0x0               | Index Invalidate           | 指令 cache |

| 0x1               | Index Writeback Invalidate | 数据 cache |

| 0x5               | Index Load Tag             | 数据 cache |

| 0x9               | Index Store Tag            | 数据 cache |

| 0x11              | Hit Invalidate             | 数据 cache |

| 0x15              | Hit Writeback Invalidate   | 数据 cache |

表 3-8 龙芯处理器的 cache 指令操作

#### 3.8 例外处理

32 位龙芯处理器具有多个例外来源,包括 TLB 缺失、整数溢出、IO 中断以及系统调用等,当处理器检测到任意一个例外时,正常的指令执行流程将被打断,处理器进入内核模式进行例外处理。

处理器进入内核模式之后,将自动禁止中断,并强制跳转到一个固定的入口地址开始执行例外处理程序;例外处理程序首先保存发生例外时处理器的上下文,包括 PC 值、当前工作模式、中断状态(使能或者禁止)等,当完成例外处理时,处理器将恢复为已保存的上下文现场。

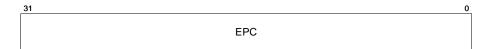

当发生一个例外时,CPO 寄存器中的 EPC(Exception Program Counter)寄存器值将被更新为例外处理之后继续执行程序的第一条指令 PC 值。如果是一条普通指令引起了例外,则 EPC 保存的是该指令的 PC 值;如果是一条延时槽指令引起了例外,则 EPC 保存的是延时槽指令之前的转移指令 PC 值。为了区分这两种情况,例外处理程序可以读取 Cause 寄存器中的 BD 位进行判断。

#### 3.8.1 精确例外

当发生一个例外时,当前指令以及流水线中所有后续指令都将被取消,不会产生有效的 执行结果并影响到处理器状态,相应地,所有与当前指令有关的流水线停顿以及潜在例外都 不会再产生作用。

在一条指令从取指到提交的流水线执行过程中,不管在哪个流水阶段发生了例外,该指令以及后续指令都将会被取消,并且在该指令到达提交阶段之后,该指令的例外信息将更新例外处理有关的 CPO 寄存器,包括例外原因、当前指令 PC 值等,此后处理器跳转到例外入口地址开始执行例外处理程序。

通过以上实现方式,当一条指令发生例外时,该指令之前的所有指令都可以完成执行,而该指令之后的所有指令都不会完成执行,因此 EPC 寄存器(或者 ErrorEPC 寄存器及 DEPC 寄存器)中保存的信息可以在例外处理之后使得程序恢复正常执行。当多条指令发生例外时,

这种方式也保证了发生例外的顺序与指令执行的顺序一致,流水线中后面的指令不会先于前面的指令发生例外。根据以上描述,由于龙芯处理器中例外处理精确对应到发生例外的指令,因此是一种精确的例外处理方式。

# 3.8.2 例外优先级

在龙芯处理器中执行指令的过程中,根据上下文情况,可能发生多种例外,表 3-9 中根据优先级列举了龙芯处理器中所有可能的例外;当同时发生多个例外时,具有最高优先级的例外将最先得到响应。

| 优先级 | 例外助记符     | 例外描述                        |

|-----|-----------|-----------------------------|

|     | Reset     | 系统复位                        |

| 高   | DSS       | 片上调试例外: 单步执行                |

|     | DINT      | 片上调试例外:调试中断                 |

|     | Int       | 中断                          |

|     | DIB       | 片上调试例外: 指令断点                |

|     | AdEL      | 取指地址错误                      |

|     | TLBL      | 取指 TLB 缺失或取指 TLB 无效         |

|     | DBp       | 片上调试例外: 软件调试断点              |

|     | Sys       | 系统调用                        |

|     | Вр        | 软件断点                        |

|     | СрU       | 协处理器不可用                     |

|     | RI        | 非法指令                        |

|     | Ov        | 整数溢出                        |

|     | Tr        | 系统自陷                        |

|     | DDBL/DDBS | 片上调试例外:不带有数据比较的数据硬件断点,      |

|     | DDBL/DDB3 | 或者带有数据比较的 store 指令数据硬件断点    |

|     | AdEL      | load 指令数据访问地址错误             |

|     | AdES      | store 指令数据访问地址错误            |

|     | TLBL      | load 操作引起的 TLB 缺失或者 TLB 无效  |

|     | TLBS      | store 操作引起的 TLB 缺失或者 TLB 无效 |

|     | TLBM      | TLB 修改错误                    |

| 低   | DDBL      | 片上调试例外:带有数据比较的 load 指令数据硬   |

|     | DDBL      | 件断点                         |

表 3-9 龙芯处理器例外优先级

#### 3.8.3 例外处理入口

在龙芯处理器中,复位作为一种例外进行处理,并且例外处理的入口地址固定为 0xBFC0\_0000。对于调试例外,根据 ECR 寄存器中 ProbTrap 位是 0 还是 1,例外处理的入口地址分别固定为 0xBFC0\_0480 或者 0xFF20\_0200。除此之外,所有其他例外的入口地址由一个向量基址与一个向量偏移值相加组合而得,如表 3-10 与表 3-11 所示;其中对于向量基址值,根据 Status 寄存器中 BEV 位的不同,该值也会存在不同。

|                   |            | BEV         |             |  |

|-------------------|------------|-------------|-------------|--|

|                   | 7017       | 0           | 1           |  |

| 1                 | Reset      | 0xBFC0_0000 |             |  |

| 3国2-4 <i>4</i> 司万 | ProbTrap=0 | 0xBFC0_0480 |             |  |

| 调试例外              | ProbTrap=1 | 0xFF20_     | 0200        |  |

|                   | 其他         | 0x8000_0000 | 0xBFC0_0200 |  |

表 3-10 龙芯处理器例外入口的向量基址

表 3-11 龙芯处理器例外入口的向量偏移量

| 例外     | 向量偏移量 |

|--------|-------|

| Reset  | 无     |

| TLB 重填 | 0x000 |

| 其他     | 0x180 |

#### 3.8.4 通用例外处理

除了复位与调试例外,龙芯处理器的其他例外均具有相同的基本处理流程,主要包括如下几个方面:

- 如果 Status 寄存器的 EXL 位为 0,则 EPC 寄存器和 Cause 寄存器中的 BD 位根据当前指令是否为转移指令的延时槽指令进行相应更新;如果当前指令不是延时槽指令,则 EPC 寄存器更新为当前指令的 PC 值,BD 位更新为 0;如果当前指令是延时槽指令,则 EPC 寄存器更新为 PC-4,BD 位更新为 1。如果 Status 寄存器的 EXL 位为 1,则 EPC 寄存器与 Cause 寄存器的 BD 位均不会更新;

- 根据具体的例外类型, Cause 寄存器中的 CE 位与 ExcCode 位更新为相应的值;

- Status 寄存器的 EXL 位更新为 1;

If Status<sub>EXL</sub>=0 then

else

● 处理器从适当的例外入口地址开始执行例外处理程序。

EPC 寄存器中的值代表了完成例外处理之后处理器恢复执行正常程序的第一条指令 PC,正常情况下例外处理程序不需要修改该寄存器的值。除非例外处理程序需要知道发生例外的指令是否是一条转移指令的延时槽指令,否则并不需要查询 Cause 寄存器的 BD 位。

另外,对于特定的某个例外,可能会保存某些额外的现场信息到其他相关 CPO 寄存器中,并由例外处理程序根据这些信息进行不同的处理。

通用例外处理的操作过程可表示如下:

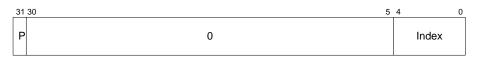

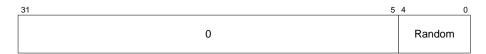

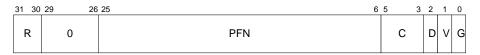

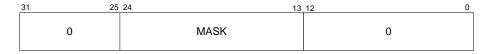

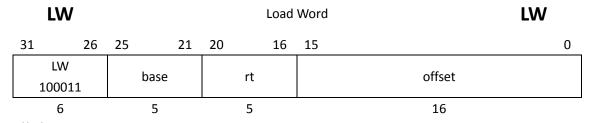

```